Vägen till 100 A vid lastpunkten och bortom

Dagens processorer är förvisso ytterst kraftfulla, men de är också mycket känsliga och kräver matningsspänningar på 1 V och lägre. Samtidigt förbrukar de mer än 100 W, vilket betyder att de kräver strömmar på över 100 A. I mindre apparater är detta en stor utmaning för effektingenjören. Dr Fariborz Musavi från CUI berättar här hur dessa strömmar kan levereras fram till lastpunkten (point-of-load).

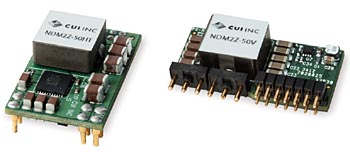

Två versioner av moduler ur NDM2Z-serien från CUI.

Moores lag har gett oss enorma mängder beräkningskraft i form av avancerade mikroprocessorer och FPGAer. Den enorma ökningen av antalet transistorer har gjort det möjligt att implementera flera snabba processorer på ett och samma chip, och alla kan köras med hastigheter på upp till 3 GHz.

De transistorer som används i dagens processorer och FPGA-kretsar är en tiopotens mindre än de som användes för bara tio år sedan. Detta har tvingat utvecklarna att minska matningsspänningarna till kretsarnas kärnor ända ned till 1 V eller mindre.

Högre spänningar skulle skada de snabba logiktransistorerna oreparerbart. Det har medfört att spänningar i området 1,8 till 3 V bara används för speciella I/O-kretsar som hanterar kontakten med minne och periferifunktioner.

Men det maximala effektbehovet hos dessa serverprocessorer och FPGAer ligger fortfarande på tiotals watt, och för de mest kraftfulla produkterna ligger det över 100 W. Detta medför att den nödvändiga strömstyrkan börjar överskrida 100 A vid lastpunkten (POL – point-of-load).

Fig 1. Dagens högpresterande FPGA-kretsar och mikroprocessorer kräver höga strömmar vid låg och strängt kontrollerad spänning.

Den traditionella ansatsen

De nödvändiga ändringarna skulle kunna införas i traditionella arkitekturer genom att man gav mer utrymme åt POL-omvandlare och avkopplingskondensatorer. Men i många av dessa avancerade system ökar inte det tillgängliga kretskortsutrymmet, utan det snarare minskar.

Ytterligare ett problem är att det krävs specialkompetens för att konstruera tillförlitliga effektomvandlarkretsar som klarar de höga strömmarna, och denna kompetens har knappast de team som konstruerar kretskort för dessa avancerade processorer och logikkretsar. Saknar konstruktören erfarenhet av denna speciella typ av konstruktioner är det stor risk att resultatet blir allt annat än optimalt.

Uppgiften att leverera effekt med låga spänningar och höga strömmar till en POL kompliceras av att de ledningsrelaterade förlusterna är proportionella mot kvadraten på utströmmen (I2out). Viktiga bidragsgivare härtill är DC-resistansen hos induktorerna, liksom effekttransistorerna och ledningsdragningen. Ett annat problem är switchningsförlusterna. Under övergångsfaserna är styrswitchens förluster proportionella mot Iout×Ein och omkopplingstiden.

Hur snabbt switchningsövergången kan ske bestäms delvis av avstängningstiden för effekttransistorns gate. Hastigheten begränsas av en ströinduktans som uppstår i vanliga MOSFET-kapslar. Genom denna induktans kan MOSFETen fortsätta att leda ström, trots att gate-spänningen gått ner till 0 volt. Orsaken är att ströinduktansen genererar en negativ mot-EMK som drar ner source-spänningen till en negativ nivå relativt gaten.

En annan ansats krävs

Förbättringar av kretsarnas Rds(on), switchningsegenskaper och drivmekanismer har givit så goda resultat att det är svårt att uppnå några större förbättringar med traditionella konstruktionsmetoder. För att klara av låga spänningar och höga strömmar krävs ett nytt sätt att se på buck-omvandlaren.

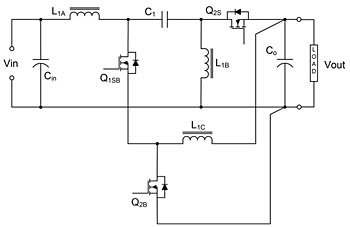

Att gå över till en SEPIC-matad buck-topologi (SFB) skulle t ex i hög grad förbättra verkningsgraden och transientsvaret, samtidigt som man bibehåller enkelheten och de låga kostnaderna hos en synkron buck-omvandlare. Man löser problemen såväl med konduktivitetsförlusterna (summan av ledningsförluster och induktorernas DCR-förluster) som med switchningsförlusterna. För att lösa problemet med I2out×R-förluster i buck-omvandlaren kan man dela upp strömmen till lasten på flera matningsbanor. Detta minskar ledningsförlusterna med kvadraten på strömminskningen.

Fig 2. Detta schema över en SEPIC-matad buck-topologi visar de båda strömbanorna.

Uppdelade strömbanor

Ett sätt att reducera förlusterna genom induktorerna vid lägre pulsförhållanden är att minska DC-resistansen genom att använda en topologi med uppdelade strömbanor.

Flera strömbanor är en fundamental ansats i SEPIC-matade buck-topologier, och den minskar spänningspåkänningarna på komponenterna med nästan 50 procent. Det medför att man kan använda MOSFETar och kondensatorer med lägre spänningsspecifikationer än vad som krävs i vanliga buck-konstruktioner.

Eftersom kretsar för lägre spänningar brukar ha högre konduktivitet går det med denna topologi att använda MOSFETar med lägre kanalresistans än vad som krävs i rena buck-konstruktioner, vilket ytterligare minskar ledningsförlusterna. Om man använder en kombinerad SEPIC/buck-konstruktion går det också att dra inström och leverera utström kontinuerligt. När buck-sektionen är bortkopplad är SEPIC-omvandlaren aktiv, och tvärtom.

Ökningarna av verkningsgraden är inte bara ett resultat av de minskade ledningsförlusterna. SEPIC/buck-topologin löser också ett antal problem med switchningsförluster i vanliga buck-omvandlare, t ex fördröjningen vid avstängning av gaten.

Dessutom går det att uppnå ytterst korta avstängningstider genom att utnyttja att topologin har en mekanism för utvinning av gate-laddning som också motverkar den mot-EMK som orsakas av ströinduktanser i sourcen. Tack vare de lägre spännings- och strömpåkänningarna på effektswitcharna kommer även tillslagsförlusterna hos dessa att minskas avsevärt.

Snabbare switchning och mindre, passiva komponenter

De minskade strömstyrkorna medför att de integrerande induktorerna och den ökade reset-spänningen ger effektsteget avsevärt snabbare respons. Dessa fördelar får ännu större betydelse vid högre switchningsfrekvenser, vilket förbättrar den totala effekttätheten.

Tester som vi har utfört på denna topologi (marknadsförd av CUI som Solus Power Topology) visar, att även om man använder samma switchningskomponenter som man använder i buck-konstruktioner, ger den SEPIC-matade buck-topologin möjligheter att minska switchningsförlusterna med mer än 90 procent. Det medför att en sådan omvandlare kan arbeta med högre switchningsfrekvens och dra fördelarna av att man kan använda passiva komponenter som är mindre.

Arkitekturen gör ytterligare fördelar i konstruktioner som ger låga utspänningar från en högre mellanspänning. Om omvandlingsfaktorn M mellan utspänning och inspänning ökas från 0,100 till 0,250 ger denna topologi förluster som är bättre än hos en konventionell buck-regulator (91 resp 88 procent). Om man ökar faktorn till 0,660 ökar verkningsgraden med 70 procent. Detta gör topologin ytterst väl lämpad för POL-applikationer som kräver stora omvandlingsfaktorer.

Fig 3. Jämförelse mellan switchningsförlusterna hos en vanlig buck-omvandlare och den SEPIC-matade buck-topologin hos Solus-arkitekturen.

Överslängar

Kravet att dessa system med höga strömmar och låga spänningar skall ge hög energiverkningsgrad innebär att processorena och stödlogiken ofta måste gå ned i lågeffektsmoder. Men de måste kunna återgå till full effekt ytterst snabbt, och utan att det uppstår några spänningsavvikelser.

En sådan avvikelse på bara två procent kan leda till ett tillfälligt avbrott, som gör att webbsökningar och VoIP-förbindelser avbryts och därmed minskade intäkter för operatören. Snabba transientsvar och hög leveranssäkerhet har avgörande betydelse i dessa system med krav på hög tillförlitlighet.

Men den minskade strömmen i induktorerna ger också förbättrade transientsvar. Eftersom strömmen genom de integrerade induktorerna nästan halveras, i förhållande till lastströmmen i varje steg, kan lastströmmen öka nästan dubbelt så snabbt jämfört med en vanlig buck-omvandlare.

Vid spänningsändringar kan strömmen sjunka nästan fyra gånger snabbare i en SEPIC-matad buck-omvandlare än i en vanlig buck-omvandlare när switchen stängs av. Därför blir effektomvandlaren snabbare under båda dessa tillstånd. Det förbättrade transientsvaret gör att såväl antalet avkopplingskondensatorer som storleken på dessa kan minskas, vilket ger ytterligare besparing av kretskortsytan.

Lägg till digital styrning

Denna topologi löser många av dagens problem med spänningsavvikelser under transienta lastförändringar och ger stabil drift, speciellt vid snabbt förändrliga förhållanden. Men genom att kombinera topologin med en avancerad digital effektstyrkrets kan man skapa ett digitalt styrt effekt-subsystem.

Det blir då möjligt att implementera mycket mer avancerade kompenserings- och styrfunktioner än vad som är möjligt med traditionella konstruktioner baserade på analoga kretsar. En annan fördel med digitala switchningsregulatorer är att det blir enklare att automatiskt optimera kretsarnas prestanda.

Kompenseringsfunktionen i digitala spänningsregulatorer har hittills implementerats manuellt i form av PID-styrslingor (Proportional, Integral, Differential). Till en början utfördes detta genom att ingenjören matade in alla externa komponenter i ett verktyg, vilket sedan beräknade PID-värden. Varje komponents uppträdande styrdes av koefficienter, och kombinationen av alla komponenter bestämde uppträdandet hos regulatorn. Denna metod var bättre än en analog metod, men den var statisk och mer anpassad för värsta-fallet-tillstånd.

Dynamisk styrning med digitala PID-slingor, där koefficienterna kunde programmeras dynamiskt, gjorde det möjligt att konfigurera och styra regulatorns prestanda i realtid och under exakta tillstånd. Detta gav mer stabilt arbetande kretsar och gjorde att systemets uppträdande kunde övervakas. Regulatorns prestanda kunde också anpassas under produktens hela livslängd. En fördel med digitala lösningar är att man kan använda flexibla styrarkitekturer, t ex med flera slingor som arbetar parallellt.

Den SEPIC-matade buck-topologin behöver en digital styrkrets som bättre överensstämmer med svarsmöjligheterna och de totala prestandaförbättringarna. Men denna funktionalitet byggs nu in i några av de senaste PWM-styrkretsarna – t ex Intersils ChargeMode-teknologi som används i deras digitala tvåfasstyrkrets ZL8800, liksom i CUIs senaste omvandlare. Den nollkompenserade ZL8800 stöder en kombination av enhetliga och flerhastighets slingstyrkretsar, en teknik som gör det möjligt att uppnå stabil effekt men samtidigt kunna reagera snabbt på plötsliga förändringar av förhållandena.

Kompensatorn inuti styrkretsen har två parallella vägar för bearbetning av en felspänning som samplas med hög hastighet. Den ena kallas den ”snabba vägen”, och den samplar oftare än den ”långsamma vägen”. Med denna nya kompensatorstruktur återkopplas kommandot för pulsförhållandet så att det går att bestämma effektverkan för den snabba vägen och upphäva denna verkan i efterkommande cykler. Med denna strategi går det att lokalisera resultatet av en spänningsförändring till ett fåtal cykler och på så sätt förhindra den instabilitet som uppstår med mindre sofistikerade PID-styrstrategier som har optimerats för korta svarstider.

X-, Y- och Z-axlarna

Genom dessa förändringar av den interna arkitekturen går det att ta fram ytterst kompakta och effektiva POL-omvandlare. Men trots det finns det fortfarande en stark önskan att få fram ännu mindre spänningsaggregat. Ingenjörerna pressas nästan alltid hårt för att hålla kretskortsytan så liten som möjligt, och det är svårare att hitta utrymme där än att hitta en ledig tomt på Manhattan. Men det kan finnas vägar att välja.

Ett mål när man tar fram en kraftmodul är att skapa en kompakt formfaktor som maximerar fördelarna hos de X-, Y- och Z-dimensioner som finns tillgängliga. När vi nu går mot strömmar på 100 A och mer kommer ingenjörerna att se mer kreativt på saken och inte bara begränsa sig till kretskortsytan, utan istället utnyttja hela kretskortsvolymen. Företagen går nu in för att uppfylla dessa behov, t ex genom att erbjuda

POL-omvandlare med två olika formfaktorer: en platt (lågprofils) och en höghusbyggd (ytbesparande) variant av varje produkt så att det går att utnyttja varenda tillgänglig kubikmillimeter. Ibland är Z-axeln obegränsad, medan den ibland är ytterst begränsad. Alla möjligheter måste täckas in av dagens produkter.

Sammanfattning

Moores lag har givit oss enorma mängder beräkningskraft. Men samtidigt som känsligheten hos dagens processorer har pressat ned spänningarna till under 1 volt kräver de mest kraftfulla produkterna effekter på 100 watt och mer. Det betyder att strömbehovet börjar överskrida 100 ampere.

Utrymme är en kritisk faktor, så traditionella metoder som använder större komponenter för att klara de höga påkänningarna är inte några realistiska lösningar. Istället krävs det innovationer och abstrakt tänkande inom många områden.

2014 kommer att bli ett extra viktigt år för leverantörerna av kraftaggregat. På APEC/PCIM har några av de första produkterna som implementerar nästa generations topologier visats upp, och produkter som SEPIC-matade buck-omvandlare börjar komma ut på marknaden. Dessa ger oss möjlighet att hantera strömmar på 60 A – och till och med 90 A – i ett enda steg. Andra halvåret 2014 kommer därför att bli extra intressant för alla som följer dessa teknologier.

Dr Fariborz Musavi, CUI

Filed under: Stromforsorjning