Temperaturkolla din ASIC eller ASSP

Det blir allt viktigare att långsiktigt kunna förutse tillförlitligheten i ASIC (Application Specific Integrated Circuits) eller ASSP (Application Specific Standardprodukter). Kretsarna tillverkas med allt mindre litografier, körs med högre hastigheter och avger mer värme i allt mindre kapslar.

Vad kan gå då gå fel? Svar: Massor!

Högre prestanda fås dock till priset högre temperaturer. Och med högre temperaturer kommer lägre tillförlitlighet om man inte stor noggrannhet tar termiska hänsyn.

Halvledartillverkare har länge varit medvetna om de problem som är förknippade med värme. De flesta har sina webbplatser fulltecknade av ”application notes” och ”white papers” i anslutning till noggranna beräkningar av energisparfunktioner med utgångspunkt i värden på de termiska resistanserna QJA och QJC? (Junction-to-Ambient och Junction-to-Case). Ofta förekommer tilläggsrutor där man föreslår föreslår olika kylare att använda i marginella situationer. Allt detta hamnar i knät på användaren.

Senaste tekniksprång och en spridd användning av termiska testkretsar som utvecklats av JVD Inc på uppdrag av Thermal Engineering Associates i Santa Clara, Kalifornien, gör att halvledartillverkare och företag som konstruerar egna ASIC/ASSP-kretsar kan ligga i fronten för termiskt ingenjörskonst i kisel innan man går till produktion.

Termisk konstruktion av egna IC

I dag kan nästan vem som helst åstadkomma en termiskt riktigt konstruerad IC. Oavsett om man är konstruktör på ett kommersiellt halvledarföretag eller om man skall utforma sin egen ASIC finns det lättillgängliga verktyg för att fysiskt simulera de termiska effekterna på sin konstruktion, och det kan göras i god tid innan man spenderar några pengar på att producera sina första kiselprototyper. Termiska testchip (Thermal Test Chips, TTCs) tillåter systemkonstruktörer att fullt ut göra modeller, mäta och modifiera sina konstruktioner innan man bestämmer sig för dyrbart.

Chip mäter på plats

TTCer är speciella kiselchip (Det handlar här om analog ASIC) som används på plats för att modellera och mäta termiska prestanda på din kiselkonstruktion innan man spenderar massor av dollar på verktyg för masker och wafers. Tack vare modellering kan man avbilda flera individuella värmekällor på TTC-chipet. Dessa värmekällor är identiska med de som kommer att finnas på din slutliga IC.

Temperatursensorer, som är strategiskt utplacerade i hela TTCn, mäter exakt temperaturen på flera platser samtidigt. Värmekällorna kan moduleras för att efterlikna olika delar av din IC när strömmen är på, av eller i ett mellanläge. Genom att spåra den absoluta temperaturen, eller temperaturförändringar, på i någon punkt av TTCn, kan man avgöra om en eller flera värmekällor i kombination gör att säkra driftstemperaturer överskrids för den planerade IC-konstruktion. Om temperaturen visar sig ge problem kan du gå tillbaka till din IC-konstruktion och modifiera chip-layouten för att isolera värmekällorna och minska det potentiella problemet.

Hur den är utformad?

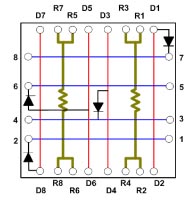

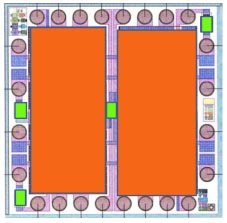

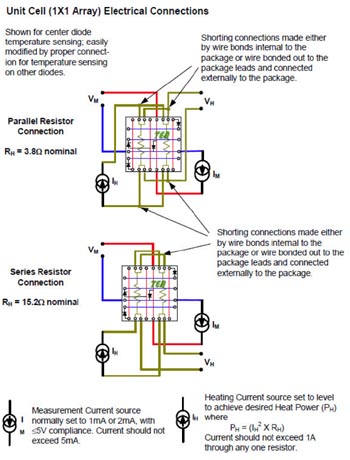

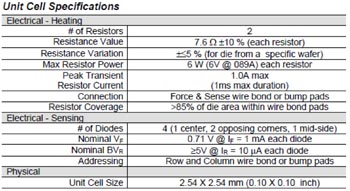

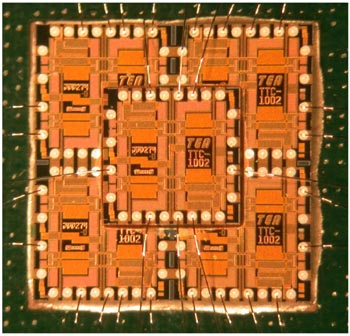

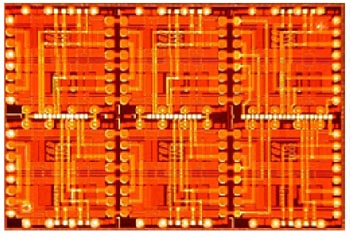

TTCer tillverkas som alla andra Analog ASIC. I detta exempel mäter varje cellen 2,5×2,5 mm och varje cell innehåller två värmekällor (metallfilmmotstånd) och fyra strategiskt placerade temperaturgivare (dioder). Se fig 1a och 1b.

Fig 1a. Grunduppbyggnaden för en TTC-cell. Lägg märket till den strategiska placeringen av temperaturavkännande dioder.

Fig 1b. Utgångspunkten för cell-layouten i en TTC. Varje cell har två resistorer som värmekällor (vilka visas i orange) och som tar upp 86 procent av kiselytan innanför kontaktanslutningarna. De fyra temperaturavkännande dioderna visas i grönt.

Det är sällsynt att en termisk analys skulle behöva utföras på en kiselbricka så liten som 2,5×2,5 mm. Av detta skäl är alla cellerna på wafern sammankopplade. Detta är viktigt eftersom termisk modellering och mätning måste göras med ett kiselbricka som ligger nära i storlek (massa) av den IC som simuleras. Wafern kan sedan sågas i någon av hundratals olika verktygskonfigurationer, som sträcker sig från en enda cell (2,5×2,5 mm) upp till en matris av 10×10 celler (25,68×25,68 mm) eller ännu större, för att få en storlek som står i proportion med IC som simuleras.

Så fungerar det

Metallfilmsmotstånd värmekällor valdes för ge bättre likformighet och anpassning över wafern jämfört med resistorer av polysilikonmasker. Dessutom resulterar deras relativt stabila temperaturkoefficienter ±20 ppm/°C i konstant effektförlust under loppet av den termiska mätningen.

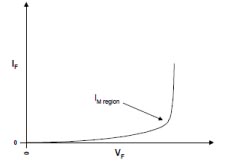

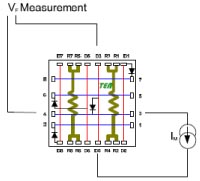

Värmekällor täcker 86 procent av kiselytan, vilket överensstämmer med JESD51-4 standarden. Varje värmekälla har ett par kontakter för strömanslutning och ett andra par av kontakter för Kelvin-anslutningar (t ex 4-trådsanslutning) för att mäta exakt den spänning som appliceras på värmekällan. Likaså har även var och en av de temperaturkännande dioderna Kelvin-anslutningar. Det gör att ett par anslutningar kan ge tillräckligt med bara framström för att styra ut dioden till under den punkt på ström/spänningskurvan där självupphettning inträder, medan det andra parets anslutningar kan mäta exakt framspänning. Det är viktigt att behålla arbetspunkten under självupphettning eftersom man annars kan få problem med repeterbarhet. Se fig 2a och 2b.

Fig 2a. Korrekt mätström, IM, visas ovan. Denna motsvarar diodens kurva för framström/spänning.

Fig 2b. Kelvin-anslutningar för temperaturkännande dioder (mittdiod kopplad i detta exempel).

Skapa och konfigurera matriser av TTCer

Det finns två grundläggande begrepp i att skapa och konfigurera TTCer: Likformig uppvärmning och distribuerad uppvärmning.

Jämn uppvärmning innebär att värmekällan är konsekvent över hela ytan av formen, vilket eliminerar eventuella termiska gradienter i kiselytan. För att uppnå detta måste motstånden i varje TTC avge samma värme och måste därför passeras av samma uppvärmningsström.

Genom att konfigurera TTCer rätt, I serie, parallell eller serie/parallellkombination, kan likformig uppvärmning uppnås.

Fig 3 (nedan) ger ett exempel på hur de två värmeelementen i en TTC kan konfigureras: Antingen parallellt (för en värmeresistans på 3,8 ohm), eller i serie (för en värmresistans på 15,2 ohm).

Fig 3. Konfigurering av en TTC.

De flesta chipkonstruktörer strävar efter att uppnå en slutprodukt vars kiselbrickor har ett längd/breddförhållande på 1:1.

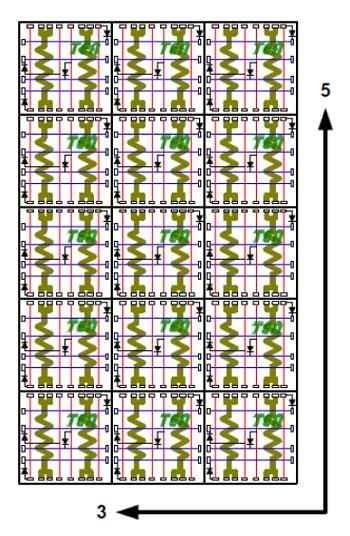

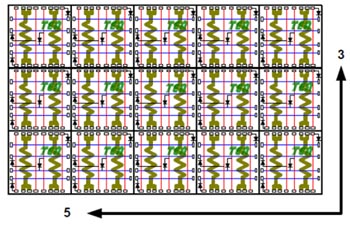

Ibland inte det möjligt på grund av I/O-krav (utplacering av bondytor). När en asymmetrisk TTC-matris behövs bör man ta hänsyn till matrisen geometri. Tag som exempel termisk simulering av en kiselbricka med måtten 13×8 mm. Detta kan uppnås genom användning av en TTC-matris som är 5×3 celler eller 3×5 celler.

Båda innehåller samma antal celler och kan därför leda bort samma mängd effekt och båda har en centrumdiod för temperaturavkänning. För att få en jämn uppvärmning fungerar båda på samma sätt. Den enda skillnaden skulle vara är den spänning och ström som behövs för att generera samma effektförlust.

Tag som exempel fig 4.

Fig 4. En 3×5 TTC-matris.

3×5-matrisen har fem seriella strängar av motstånd där varje sträng har en resistans av cirka 37,5 ohm ( 5×7,5 Ohm). Parallellkoppling av dessa strängar resulterar i en total resistans på omkring 6,25 ohm. För 10 W effektförlust skulle det behövas en spänning på 7.9 V @ 1.265 A.

Den 5×3-matris, som visas i fig 5, har 10 seriesträngar med tre motstånd där varje sträng har en resistans av cirka 22,5 ohm (dvs 3×7,5 Ohm). Parallellkoppling av dessa strängar resulterar i en total resistans på omkring 2,25 ohm. För 10 W effektförlust skulle en spänning på 4,74 V @ 2,1 A krävas.

Fig 5. En 5×3-matris.

Båda tillvägagångssätten fungerar. Men det är bättre att välja alternativet för lägre ström eftersom detta innebär lägre påfrestningar och kräver mindre ledningsbredder på det substrat där det kapslade chipet är monterat.

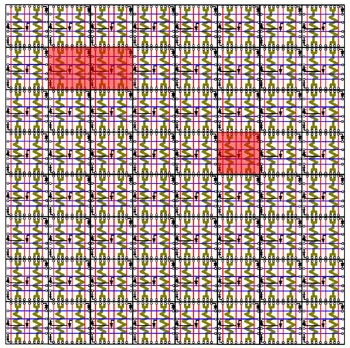

Distribuerad uppvärmning är faktiskt mer representativt för vad man kan förvänta sig att se i en stor ASIC eller ASSP. Vissa delar av kretsen som är konstruerade för högre hastighet, eller som måste hantera större effekt, förväntas leda bort mer värme. Chip-konstruktörer kommer att vilja veta hur varma dessa ”hot spots” faktiskt blir och hur värmen kan påverka kretsar på ett annat ytor av chipet. Dessa kretsar kan exempelvis vara känsliga för värme, till exempel en precisionsspänningsreferens.

TTCer är utformade för att passa för antingen trådanslutna eller med lödkulor (”bumps”) försedda flip chip.

I konfigurationen trådanslutna är anslutningsytorna (”pads”) runt varje TTC ansluten till dess intilliggande granne med metall. Först när kiselbrickan är sågad till önskad form (2×2, 5×5, 7×9 etc) är anslutningen avhuggna.

Konventionella trådförbindningstekniker begränsar till stor del åtkomsten av utgångarna till de som kan nås i matrisens periferi. På grund av det sätt maskningen görs av skivorna är den största chipstorlek på trådbondade chip en 40×40-matris (1 600 TTCer upptar sammanlagt 10,000 mm2 yta vilket motsvarar ungefär 100×100 mm).

När en tillämpning kräver att man mer lokalt undersöker uppvärmning, för att kartlägga effektdensitet, är flip chip-konstruktionen idealisk. Utan interna anslutningar mellan TTC i matrisen är alla förbindningsytor tillgängliga. Tag som exempel en 8×8 TTC-matris där värme kan alstras vid utvalda celler. Se figur 6.

Fig 6. Individuella celler kan effektsättas för att stimulera partier av hög effektavgivning hos ICn. Temperaturavkännande dioder i dessa, och alla andra celler, kan sedan användas för att mäta det värme som brer ut sig på kiselytan.

Det är viktigt att specificera cellenheterna i varje TTC, detta för att övergripande kunna förstå förväntat resultat av den matris som används för att simulera den nya IC som skall utvecklas. Se fig 7.

Fig 7. Specifikationer för en cellenhet.

Förutom enstaka chip-kapslar, kan TTC även erhållas i kundanpassade, staplade konfigurationer (se fig 8) samt flerchips (horisontell uppställning) kapslar samt kapsel-på-kapsel-komponenter. Kundanpassad kapsling kan också ges i de krav inte uppfylls i de standardkapslingar som beskrivs ovan.

TEA har nyligen infört ett nytt format av TTC-cellstorlek som är 1×1 mm och som innehåller ett enda värmemotstånd och en enda temperaturkännande diod. Den mindre enhetscellen möjliggör större effektkartläggning. Båda storlekarna av TTC-enhetsceller finns på 150 mm (6 tum) wafer liksom utsågade matris-chip.

Fig 8. Mosimage. Trådbondade 1×1-chip monterade på ett trådbondat 2×2-chip

Metallager för omkoppling

En RDL (Re-Distribution Layer) används för att omfördela de elektriska kontakteringsytor (”pads”) – antingen med trådbondningar eller lödkulor – i en annan konfiguration än den ursprungliga chipkonfigurationen. Några anledningar till detta är:

* När man vill montera ett chip på en BGA-kapsel vars substrat ursprungligen varit avsett för en annan chip-pad-konfiguration.

* Trådbondade chip kan ha en enda rad av anslutningsytor för trådbondning i centrum av chipet.

* Stackade chip kan kräva att alla trådbindningsytorna ligger längs en av chip-kanter.

Processen för att skapa en RDL på skivan består av att skapa ett eller flera metallskikt mellan isoleringsskikten. Metallskikten är etsade för att bilda spår som förbinder befintliga chip kontaktdynor till skapat nya kuddar i önskade platser. Beroende på trace routing komplexitet, kommer det att finnas flera skikt av metall och isolator staplas på en annan. De nya dynor kan användas för trådbondanslutning eller fungera som bas för att lägga Flip Chip gupp.

Fig 9 är en TTC-1002 2×3 matris med en RDL som sörjer för trådbondning, antingen längs specifika platser i periferin eller ner i mitten av chipet. Den RDL är en anpassad krav som måste diskuteras i detalj med TEA innan genomförandet kan påbörjas.

Fig 9. Omkopplingslager för anslutningsytor.

Hur varmt är varmt?

Genom att beräkna effekttäthet med hjälp av empiriska data från termiska testchips kan IC-konstruktörer och kapslingsingenjörer modellera det faktiska utförandet av en produkt i god tid innan han har tagit steget från konstruktion av kisel eller en kapsel till reell verklighet. Utvecklingen inom halvledarprocesser går mot att jämka samman hittills oförenliga bitar av komplexa system på ett enda substrat. Borta är de dagar då effektkomponenterna isolerades till sina kapslar för kylfläns. Nu bor de några få mikrometer bort från temperaturkänsliga strukturer. Någon måste ge seg. Eller inte?

Användningen av Thermal Test Chips tillåter konstruktörer att exakt lokalisera värmekällorna i sina konstruktioner och simulera hur de påverkar resultatet för hela systemet. Tag den 2,54×2,54 mm stora enhetscell som diskuterats tidigare. Med sina två 7,6 ohms motstånd som värmeelement, som var och en kan hantera 1 A vid 6 V, kan cellen avge 12 watts effekt. Dess yta (6,45 mm2) ger en effekttäthet på 186 W/cm2. Den nyligen införda 1×1 mm stora enhetscellen med sitt enda 10,5 ohms motstånd som värmeelement, som kan hantera upp till 0,55 A vid 5,5 V, kan avge 3 Watt. Med dess yta på 1 mm2 innebär det en effekttäthet på 300 W/cm2.

Om man kombinerar enhetsceller till en matris kommer dessa siffror att minska något eftersom det krävs extra kisel för att såga gator mellan cellerna. Till exempel har en 10×10 matris av 6,54 mm2 celler en effekttäthet på 182 W/cm2, medan en 10×10 matris med 1 mm2-celler har en effekttäthet på 261 W/cm2. Dessa är exceptionellt höga PD och är svåra att nå på annat sätt.

Vid kartläggning av effekt kan dessa höga effektdensiteter erbjuda användaren en möjlighet att bättre simulera de nivåer av effekttäthet som är följden av flera punkters lokal uppvärmning, som från högpresterande processorer och ASIC-kretsar. Dessutom kan de bättre simulera hög effekt i högfrekventstransistorer av SiC (kiselkarbid) eller GaN (galliumnitrid).

Användningen av dessa testchips för analog ASIC diskuteras sällan i allmänna tidskrifter. Men de spelar en viktig roll i att låta halvledartillverkare och företag som konstruerar egna ASIC/ASSP komma steget före, detta genom att termiskt ingenjörsarbete av sitt kisel innan det går till produktion.

Bob Frostholm, JVD Inc (San Jose, USA), ansvarig för försäljning och marknadsföring till företag för analog ASIC.

Gedigen erfarenhet

Bob Frostholm har verkat inom försäljning, marknadsföring och som vd inom etablerade och nystartade analoga halvledarföretag i mer än 40 år. Bob var en av personerna bakom den allestädes närvarande kretsen 555 – en analog universalkrets med mängder av möjliga applikationer!

Efter 12 år med Signetics-Phillips, Fairchild och National Semiconductor, var han med och att grunda sitt första uppstartsföretag 1984: Det i Skottland baserade företaget Integrated Power. Det som såldes till Seagate 1987.

Han gick därefter över till Spragues halvledarverksamhet i Massachusetts och hjälpte dem att knoppa av sin halvledargrupp och skapa vad som nu heter Allegro Microsystems. Senare hjälpte han LSI Logic att överta SEEQ Technology.

Bob har verkat som konsult för många nystartade bolag innan han han anslöt sig till JVD år 2010. Han är författare till flera tekniska artiklar och vitböcker. Email: bob.frostholm@jvdinc.com

Filed under: Analogteknik