Svenska IP-block ger snabbare SoC

Problemet med att effektivt dela minne i en SoC med många processorer löser det svenska företaget Elsip med tre IP-block, utvecklade av tre forskare vid KTH. På FPGAworld presenterade Elsip sin nya produkt ”DME for Zynq" som tar hand om minneshanteringen i programmerbara kretsar i Zynq-familjen från Xilinx.

På bilden ser vi Bengt Edlund, affärsutvecklare och försäljningsdirektör i Elsip, och Adam Edström, vd för Elsip. De gick in i företaget 2012 med syfte att kommersialisera den verksamhet som de övriga tre ägarna lade grunden till. Dessa är KTH-professorerna Axel Jantsch, Ahmed Hemani och Zhonghai Lu.

Affärsidén bygger på att kommersialisera IP-block av professorernas lösning ”Data Management Engine”, DME, som bygger på många års forskning vid KTH.

Så frågan är, kan man skydda denna lösningen från att bli kopierad av andra aktörer på världsmarknaden?

– Dels är den programmerbara DME-lösningen patentsökta och mycket av NoC-teknologin presenterades av grundarna redan på 2000-talets början där de myntade ordet Network on Chip (NoC) under forskarkonferenser och därigenom gjorde det fritt att använda, säger Bengt Edlund.

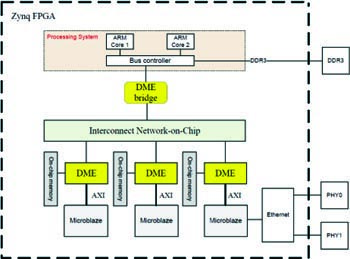

”DME for Zynq” består av tre IP-block: ”Data Management Engine”, DME, ett ”network-on-chip”, NoC för kommunikation mellan olika noder, och en brygga (modifierad DME) som ansluter ARM-kärnor i Zynq med Microblaze-kärnor (en ”mjuk” processorkärna, ursprungligen utvecklad i Sverige för Xilinx) och med andra IP-block av logiska grindar i Zynq-kretsen. Så här kan det se ut:

DME skapar en global och enhetlig minnesrymd med möjlighet till synkronisering, kommunikation och funktioner som lätt kan förflytta data mellan minnen, innanför och utanför chippet. Som resultat blir det enkelt att skapa ett programmerbart flerprocessorsystem på en FPGA, med snabba, förutsägbara data.

– Zynq är en fantastisk krets, men för mjukvaruutvecklare innebär många processorkärnor en utmaning, inte minst om man har kravet på realtidsprestanda. Vår teknik är dessutom skalbar vad gäller antalet processorkärnor och i fråga om IP-block från tredje part, säger Adam Edström.

Realtidsprestanda krävs exempelvis i många industrisystem.

– Vår lösning kan gälla hundratals processorkärnor, eller mer, säger Bengt Edlund och visar upp en graf.

Denna visar skillnaden mellan central respektiv distribuerad minnesarkitektur. Ett distribuerat minne skalar linjärt medan centrala minnen ger problem som leder till att prestanda inte motsvarar den ökade mängden kärnor.

– Vi gör det lätt att använda distribuerade minnen och att därmed få valuta för pengarna, betonar Bengt Edlund.

DME for Zynq levereras som IP-block för en kompilerad lista i Verilog. Samma sak gäller NoC. Till det kommer programvara för DME och API. Elsip levererar också IP i form av modell i C++.Testbänken, liksom testfall av programvara, kan anpassas till kundernas krav och givetvis medföljer dokumentation.

Företaget Elsip AB grundades 2011 med ekonomiskt stöd av Vinnova. Dotterbolaget Memcon har etablerats i Wuxi, Kina, och man har ett samarbete med Fudan-Wuxi Institute i Shanghai.

Filed under: SvenskTeknik