Stort genombrott för mjukvarustyrd radio i en krets

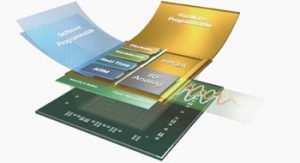

Xilinx nya programmerbara RFSoC, ”radio frequency system on a chip” innebär att man kan bygga en mjukvarustyrd mottagare med ett chip. 16 nm CMOS-halvledarprocess med FinFET har möjliggjort analoga delar med RF-prestanda. Den kompakta och mycket effektsnåla lösningen passar särskilt väl för massiv MIMO för 5G.

En direktsamplande mjukvarustyrd radio, ”software defined radio” består i princip av en A/D-omvandlare och en digital signalbehandlare, som företrädesvis är en FPGA för att möjliggöra parallell databehandling. Genom att integrera dessa byggstenar till ett system i en krets, SoC, blir det möjligt att åstadkomma mycket kompakta lösningar. Det krävs för exempelvis massiv MIMO där man använder stora tvådimensionella antennmatriser, med en mottagare i varje matrispunkt.

Xilinx nya programmerbara RFSoC innehåller omvandlarkretsar för radiofrekvens:

* En direktsamplande analog konstruktion.

* Två 12 bit A/D-omvandlare. Dessa kan konfigureras på två sätt:

Antingen som en 4 GSa/s kanal (RF-mod) eller som två kanaler (I och Q) med 2 GSa/s. Omvandlaren följs av en digital nedblandare.

Varje 2 GSa/s omvandlare består av fyra 500 MSa/s omvandlare vars signaler interfolieras (”interleaving”). Switcharna för detta kräver ingen kalibrering.

I IQ-mod behövs bara kalibrerig av offset och amplitudavvikelse.

Vid RF-mod (där I och Q i stället utvinnes i den digitala domänen – man ”tappar” 3 dB men kan undvika kalibrering) delas klockan med en faktor 2 och sänds i fas/motfas till respektive A/D-omvandlare. I detta fall används ytterligare en styrcell för att minimera tidsskillnader mellan 2 GSa/s-enheterna. Slutligen styrs varje 500 MSa/s-enhet i en kalibreringsslinga.

* 14 bit D/A-omvandlare upp till 6,4 GSa/s med digital omvandling

Låg effektförbrukning

Tack vare att de analoga kretsarna är byggda med FinFET, i en 16 nm CMOS-process, har strömförbrukningen kunnat hållas låg. I vandliga fall drar en A/D-omvandlare som denna kring 2 W och en D/A-omvandlare 1,25 W.

I det här fallet drar RF-omvandlarkretsarna 513 mW vid 4 GSa/s. Av detta står bufferkretsarna för 282 mW, A/D- omvandlarna drar 142 mW medan den digitala delen av kretsen förbrukar 89 mW.

Om vi i stället hade utgått från en FPGA-krets och separata A/D- och D/A-omvandlare hade avsevärda effektförluster tillkommit i den seriella 12,5 Gbit/s-länken enligt JESD204B-protokollet. Dessutom är denna snabba länk inte trivial att sätta upp utan distorderade signaler och förluster. Allt detta arbete bortfaller med den integrerade RFSoC-lösningen.

Figuren visar hur mycket effekt RFSoC-lösningen sparar

Xilinx ger ett exempel hur mycket effekt deras RFSoC spara i olika konfigurationer. Ju fler kanaler – desto större besparingar:

* 4 Tx × 4 Rx (4 sändare, 4 mottagare) vid 100 MHz = 41 procents effektbesparing.

* 4 Tx × 4 Rx vid 200 MHz = 37 procent effektbesparing.

* 8 Tx × 8 Rx vid 100 MHz = 51 procent effektbesparing.

Xilix började integrera högpresterande A/D- och D/A-omvandlare i sin serie 7 år 2012. Med RFSoC tar man ett radikalt steg mot en direktsamplande radiolösning när man kan undvika att behöva överföra signaler via JESD204B: Man vinner effektförbrukning och kan korta ned konstruktionscykeln.

Filed under: SvenskTeknik