Stackade FPGA-kretsar i jätteformat

– På det här sättet kan vi flytta fram positionerna en hel generation, säger Patrick Dorsey från Xilinx. Och det gör vi genom att stacka flera FPGA-chip på en kiselbärare.

Det finns alltid behov av större FPGA-kretsar. Därför görs alltid de största FPGA-chipen så stora som det är fysiskt möjligt. Flera kretsar kan naturligtvis kopplas samman på ett mönsterkort, men förlusterna är stora.

– Det går åt många I/O-anslutningar bara för internkommunikation och man tappar en hel del i hastighet. Därför har vi länge tittat på möjligheten att stacka chip på kiselbärare.

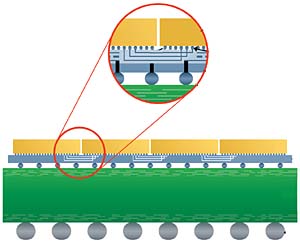

Den teknik man nu lanserar baseras på höga och smala FPGA-chip som monteras sida vid sida på ett stort kiselsubstrat. Man använder 3D-kapslingsteknik och viaanslutningar som går genom chipet (TSV). De höga och smala FPGA-chipen har plats för massor av anslutningar på långsidorna och eftersom anslutningarna via kiselsubstratet är så korta krävs minimal buffring. Totalt finns mer än 10 000 anslutningar mellan FPGA-chip och kiselsubstrat. Fördröjningen i övergången ligger bara runt en nanosekund.

Med fyra FPGA-chip sida vid sida blir förstås den maximala storleken betydligt större än vad som är möjligt i en monolitisk lösning.

– Det blir dessutom kompaktare, billigare och mera strömsnålt. Konstruktören kan använda samma verktyg som vanligt vid konstruktionsarbetet och när processteknologin har flyttats framåt ett steg blir det möjligt att gå över till en monolitisk lösning.

Virtex-7 LX200T blir den första multichips FPGA-kretsen för leverans. Den får upp till 2 miljoner logikceller, eller 2,8 gånger större kapacitet än den största monolitiska Virtex-komponenten i samma tillverkningsprocess (28 nm).

Filed under: Utländsk Teknik