Snabbt gränssnitt för dataomvandlare

Gränssnittsstandarden JESD204B för höghastighets seriella dataomvandlare ger avsevärda fördelar jämfört med parallella dataformat.

Samplingshastighet och upplösning hos dagens dataomvandlare ökar. Därför har nya högdensitetsmetoder för digitala datagränssnitt utvecklas för att klara av det stora antalet signaler och de höga hastigheterna för datatransmission. Snabba seriella gränssnitt ger många fördelar jämfört med traditionella parallella gränssnitt, men de kan vara svåra att implementera även för de skickligaste konstruktörerna.

Även om många systemutvecklare och konstruktörer inser det enorma potentiella värdet, ser de också ökande risker. Därför är de tveksamma till att införa teknologin – trots att befintliga lösningar ofta kostar mer och kräver mer utrymme och effekt.

Fördelarna med de nya gränssnitten är betydande. En övergång till ett seriellt gränssnitt minskar avsevärt antalet data- och klocksignaler. I sin tur ger det färre I/O-pinnar, färre kretskortsledningar och minskade fysiska designbegränsningar. Och förutom dessa uppenbara fördelar tillkommer även fördelar på systemnivå.

Fiberöverföring

Ett fiber/koax-uppbyggt hybridnätverk består t ex av hundratals fjärrplatser som omvandlar data från koax till fiber och sänder dem tillbaka till en central plats. På varje fjärrplats finns en A/D-omvandlare (ADC) som digitaliserar signaler från koaxkabeln. ADC-utsignalerna serialiseras och sänds sedan över fiber via en optisk sändare.

Detta kan implementeras med en traditionell (parallell) A/D-omvandlare – och en del konstruktörer gör det. Men en sådan konstruktion kräver ett extra element mellan A/D-omvandlaren och den fiberoptiska sändaren som serialiserar dataflödet, och detta element är ofta kostsamt och utrymmeskrävande.

Nu finns det ett alternativ: Genom att använda en A/D-omvandlare med JESD204B-komplianta, seriella höghastighetsutgångar kan man eliminera den serialiserande komponenten, vilket minskar sändarens storlek och effektförbrukning. Orsaken är att JESD204B-data kan sändas ut direkt över fiber.

I många fall skulle det anses vara riskabelt att använda en krets som följer en ny standard. Men det går att bygga prototyper och demonstrera denna förenklade arkitektur med hjälp av vanliga, lagerhållna utvärderingspaket för JESD204B-baserade A/D-omvandlare och en fiberoptisk sändare. Det krävs ingen extra kodning, nivåöversättning eller några serialiseringsoperationer.

JESD204B-standarden ger fördelar

JESD204B är en standard för seriella höghastighetsgränssnitt i dataomvandlare som ursprungligen introducerades år 2006. Sedan dess har den utvecklats genom tre generationer, JESD204, JESD204A och JESD204B, där varje revision har varit en förbättring av den föregående.

Två funktioner, som varit betydelsefulla för att standarden skulle anammas av kommunikations- och ADC-marknaderna, infördes i version B. För det första ger JESD204B deterministisk latens vid mappning från omvandlarens klocka till den seriella datautgången, vilket möjliggör enhetlig datalatens efter varje reset.

För det andra ökar B-versionen den maximala datahastigheten, vilket ger effektivt utnyttjande av färre I/O-resurser. B-standarden möjliggör t ex att en dubbel, 14-bits, 250 MSa/s A/D-omvandlare kan använda en enda seriell bana per kanal. Med A-versionen krävde samma datahastighet två banor per kanal, vilket dubblerar de nödvändiga I/O-resurserna.

Osäkerheten i latensen, liksom de låga datahastigheterna hos A-standarden, bromsade upp en bredare acceptans av denna standard. B-standarden kommer att påskynda detta viktiga steg framåt, med en början i applikationer inom kommunikation och flerkanaliga omvandlare.

Förenklar systemarkitekturen

Eftersom dessa avancerade A/D-omvandlare utför den serialiserande operationen går det nu att i många system eliminera speciella serialiserande kretsar, vilket minskar utrymmeskraven, effektförbrukningen och kostnaden.

Vi börjar med att se på den ovan beskrivna fiber/koax-hybridsändaren. Traditionellt består detta system av en A/D-omvandlare, som är ansluten till en FPGA, som är ansluten till en fiberoptisk sändare. FPGAn paketerar och serialiserar dataströmmen från en A/D-omvandlare med parallellutgång.

Men genom att använda A/D-omvandlare med JESD204B-utgångar går det att ta bort FPGAn och ansluta ADC-utgången direkt till den fiberoptiska sändaren. Detta minskar kostnaderna och effektbehovet vid en ofta fjärrbelägen plats, och minskar storleken på den totala lösningen.

På liknande vis kan vi se på ett radarmottagarsystem (eller vilken flerkanalig mottagare om helst) som består av ett stort antal mottagarelement vars utsignaler kräver komplex signalbearbetning. Det finns många skäl till att det vore fördelaktigt att utföra denna signalbearbetning vid någon annan plats, hundratals meter eller flera kilometer bort från antennen.

Men detta skapar två problem: för det första hur man får flera Gbit/s med digitala data från A/D-omvandlaren från mottagaren till den centrala databearbetningsplatsen, och för det andra hur man skall kunna klara detta inom de fysiska begränsningarna hos mottagaren?

Längre avstånd

Normalt kan ADC-utsignaler (LVDS/CMOS) sändas högst omkring en meter. Det betyder att dessa signaler måste omvandlas på något sätt så att det går att överföra dem över längre avstånd. Fiberoptik är den uppenbara lösningen för digital långdistansöverföring. Men utmaningen blir då att begränsa de nödvändiga I/O-resurserna med hjälp av serialisering av ADC-utsignalerna, och att sedan omvandla dessa till optiska signaler – allt inom de uppsatta utrymmeskraven.

I dagens implementeringar av båda dessa system utförs serialiseringsfunktionen typiskt av en relativt avancerad FPGA. Genom att ta bort FPGAn från enheten och istället använda JESD204B-anpassade A/D-omvandlare uppnår man stora fördelar. I ett system som en kabelsändare kan t ex FPGAn tas bort från varje fjärrplats – vilket sparar in kostnad och effekt – eftersom sändaren inte längre behöver dem.

Ett annat exempel är ett radarsystem. Här kan åtgärden att flytta FPGAn från ”front-end”-delen av konstruktionen till ”back-end”-delen vara den enda metoden för att klara av layouten av den kompletta mottagarkedjan, från RF via digital till optisk, inom det begränsade utrymme som står till förfogande. I båda dessa fall krävs dock FPGAer i systemets mottagardelar, och de förblir viktiga delar av konstruktionen.

Alternativet finns och kan demonstreras

Intersil har utnyttjat sin familj av 12- till 16-bits JESD204B-komplianta A/D-omvandlare och utvecklat en referenskonstruktion som ger kunderna dessa fördelar av minskade dimensioner, kostnader och effekt.

Med hjälp av utvärderingskort med fiberoptiska transceivrar från Avago har vi kunnat demonstrera flera olika sändarmöjligheter, däribland tvåkanals 14-bits A/D-omvandalre med två fibrer, tvåkanals 12-bits A/D-omvandlare med en fiber samt enkanals 14- och 16-bits A/D-omvandlare med två fibrer.

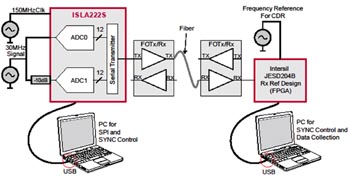

För att ta emot och analysera datamängden har Intersils referenskonstruktion med en Virtex-5-baserad JESD204B-mottagare använts. Fig 1 visar ett exempel på ett blockschema för detta system.

Bland den typ av konstruktioner som kan dra nytta av detta finns:

* Cable Digital Return, Radio-over-Fiber, Antenna Array Processing: Data digitaliseras, serialiseras och sänds sedan över en fiberkabel. Snabba JESD204B-A/D-omvandlare kan eliminera behovet av en speciell serialiseringsfunktion, vilket eliminerar eller kostnadsminskar FPGAn.

* Infrastrukturer inom kommunikation: Basstationer och fjärrplacerade ”radioheads” kräver ofta flera mottagare. Ett seriellt gränssnitt från ADC till FPGA förenklar den fysiska konstruktionen, om den snabba seriella förbindelsen har konstant latens. JESD204B-ADCer uppfyller dessa krav på latens.

* Generella I/O- och digitaliseringsmoduler: Modulära I/O-kort används ofta i icke-enhetliga konfigurationer där ett I/O-kort ansluts till ett datainsamlingskort. Dessa har ofta ett begränsat antal pinnar i kontakten. I/O-enheter med seriella höghastighetsgränssnitt möjliggör ett större antal I/O-kanaler.

Den optiska transmissionen hos JESD204B-komplianta A/D-omvandlare kan demonstreras med hjälp av lagerhållna, fiberoptiska utvärderingskomponenter och Intersils utvärderingsplattform för JESD204B.

Fig 1 visar en implementering som har visat sig vara effektiv. Här digitaliseras två insignaler av en ISLA222S, som är en 2-kanals, 12-bits, 150 MSa/s A/D-omvandlare med en seriell utgång. Utsignalen matas in på TX-ingången hos ett utvärderingskort från Avago.

Fig 1. Blockschema med en ISLA222S-krets som driver TX-ingången på ett utvärderingskort med en fiberoptisk transceiver från Avago.

Den fiberoptiska transceivern omvandlar den elektriska dataströmmen på 4,5 Gbit/s till en optisk signal och överför denna över fibern till en annan Avago-transceiver som omvandlar signalen tillbaka till en elektrisk.

Transceiverns RX-utgång är ansluten till Intersils JESD204B-moderkort, där data de-serialiseras och presenteras på Intersils referenskonstruktion för JESD204B-mottagare.

Standardisering ger mindre risk

Seriella höghastighetsgränssnitt är kända för att ge avsevärda fördelar. Men många konstruktörer tycker att de medför implementeringsrisker som man upplever som höga. Men standardiseringen av gränssnittet minskar i själva verket dessa risker. Som vi visat här kan enheter som stöder JESD204B, t o m från olika leverantörer som Intersil, Avago och Xilinx, snabbt kopplas ihop för att ge användaren de enorma fördelar som seriella höghastighetsgränssnitt ger.

Filed under: Analogteknik