Riktlinjer för att konstruera för testbarhet

När det gäller att konstruera kretskort som går att tillverka finns det ett antal olika faktorer som har stor betydelse, och detta gäller även för kostnaderna för att producera kretskort som går att testa. Som ingenjör är det viktigt att ta med i beräkningarna de totala kostnaderna för att producera och lansera ett testbart kretskort, liksom vad detta betyder för designprocessen och hur man budgeterar och planerar projektet. Chris Carlson, Senior Field Application Engineer hos Altium beskriver grunderna för DFT.

När man konstruerar för testbarhet finns det många viktiga faktorer att tänka på, som kostnaden för att tillverka själva mönsterkortet, komponentkostnaderna, monteringskostnaderna samt de kostnader som är förenade med att testa kretskortet. Det är också värt att notera att enbart kostnaden för att testa det färdiga kortet kan uppgå till nästan hälften av den totala kostnaden för att producera produkten. Detta är något som man måste ha i minnet under de inledande planeringsstegen för projektet.

Kraven på att effektivt kunna hantera komplexa produkter och utveckla de arkitekturer som behövs för att stödja dessa har fått alltfler elektronikföretag att anamma modellen ”konstruera för lönsamhet” (Design for Profitability) – dvs att optimera produkterna under konstruktionsstadiet för att uppnå strikta mål för prestanda, tillförlitlighet och säkerhet. Hur åstadkommer de detta?

Konstruktion för lönsamhet består av två huvudkomponenter. Den ena är konstruera för tillverkningsbarhet (DFM – Design for Manufacturability), vilket betyder att utveckla en produkt som har lägsta möjliga tillverkningskostnader med bibehållande av en godtagbar felfrekvens.

Den andra är konstruera för testbarhet (DFT – design for testability), vilket innebär att man lägger till tekniker och metoder som utformats specifikt för att öka en produkts testbarhet och validera dess funktionalitet och prestanda. En förståelse för hur denna modell signifikant påverkar kretskortets testbarhet hjälper konstruktörerna att förbättra kretsarnas prestanda, tillverkbarheten av deras kortkonstruktioner och kvaliteten hos slutprodukten.

Standardriktlinjer för DFM och DFT

Vid valet av en kontrakttillverkare bör konstruktörsteamet alltid tillhandahålla riktlinjer för DFM och DFT. Det är viktigt att konstruktörerna har en grundlig förståelse för dessa riktlinjer för varje potentiell tillverkare. Att noga gå igenom DFM- och DFT-riktlinjerna från olika tillverkare kan ge en insikt om varje tillverkares nivå på kompetens, kunnande och möjligheter. Det innebär att dessa riktlinjer också är till hjälp när det gäller att avgöra vilken tillverkare som är bäst lämpad att tillverka en viss produkt.

Att noga gå igenom DFT-riktlinjerna innan ett designprojekt påbörjas ger konstruktörerna möjlighet att mer effektivt planera och utforma sina layouter. Dessutom är det alltid rekommendabelt att kontakta tillverkaren direkt för att definiera projektets specifika behov tillsammans med en erfaren testingenjör.

Testtäckning

En kombination av ’Boundary Scan (JTAG), automatiserad ICT-test, röntgenlaminografi (AXI) samt både manuell och maskinell inspektion ger bästa möjliga testtäckning. Konstruktörerna får också möjligheter till omedelbar återkoppling från tillverkningsprocessen så att arbetsflödena snabbt kan anpassas efter behov och defekta komponenter lätt kan identifieras och uteslutas.

En annan faktor att beakta är vilken testtäckning som krävs för att kunna garantera kvaliteten hos en produkt, och även om det finns ett stort antal olika testvalmöjligheter kan kanske ett enkelt funktionstest vara allt som behövs.

Hur och varför ICT-test är värdefulla

ICT-test används både vid tillverkningen och på komponentnivå för att upptäcka ett antal defekter på kretskortet. Det finns två typer av ICT-testsystem:

1. Testfixtur: Ett sådant system håller testobjektet fastspänt och utför analysen med hjälp av anslutningar till olika nät på kortet.

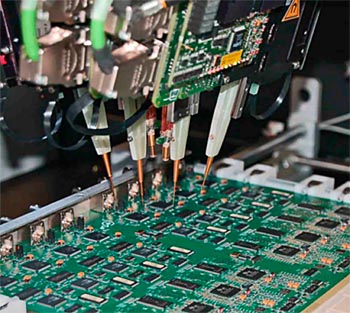

2. ”Flying-Probe”-test: Här används rörliga testprober som styrs av en dator och som skapar elektrisk kontakt med specifika nät på testobjektet.

Det finns ett antal olika feltyper som kan upptäckas, däribland komponenter som fattas, kortslutningar och avbrott, felplacerade komponenter med fel värden eller fel polarisering samt en uppsjö av andra kretsrelaterade fel. Vid ICT-test går det också att lägga på matningsspänning på testobjektet och utföra olika analoga och digitala test för att verifiera korrekt operation.

Krav vid ICT-test

När man överväger att använda ICT-test finns det specifika krav på vilka test som är lämpliga för specifika system, t.ex. om man skall använda testhuvuden eller Flying-Probe. För system med testhuvuden finns det DFT-riktlinjer som anger testvillkoren för varje testpunkt. Att ha en kopia av dessa riktlinjer tillhands underlättar mappningen och utplaceringen av layouten hos kretskortet.

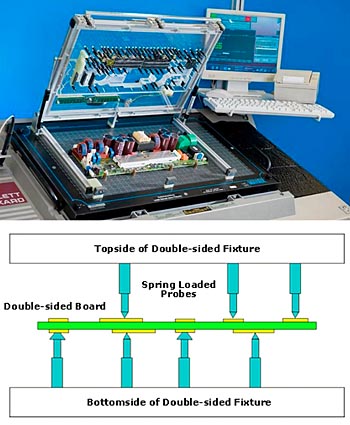

ICT-fixturen undersöker olika egenskaper hos kortet, skapar mätningar samt överför matningsspänningar, stimuli och mätsignaler till testobjektet. Testsystemen kan mäta på båda sidor av kortet, men genom att placera alla testpunkter på samma sida går det att minska komplexiteten hos fixturen. Det betyder att denna testmetod kan minska totalkostnaderna och öka lönsamheten hos slutprodukten.

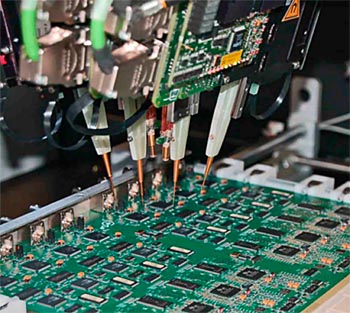

Fig 1. ICT-testfixtur

När en fixtur för ett visst testobjekt väl har färdigutvecklats kommer alla extra modifieringar i syfte att förenkla ändringar av produkten att medföra extra kostnader. Om modifieringar av testfixturen blir nödvändiga är det bäst att konstruktören lägger ned extra möda på att inte flytta positionen hos någon av de befintliga testpunkterna.

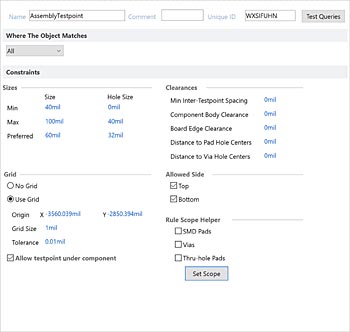

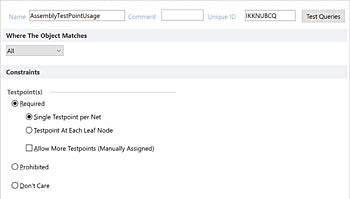

Det EDA-verktyg som används för layouten av kortet har en uppsättning designregler som definierar egenskaperna hos varje testpunkt, tillsammans med den nödvändiga testtäckningen. Genom att noggrant konfigurera dessa regler under planeringsstadiet av layouten går det att göra framställningen av testdokumentationen till en strömlinjeformad, automatiserad process.

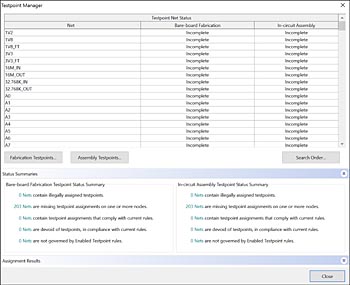

Fig 2. ICT-testregler med egenskaper och täckningsgrad för en testpunkt

Fig 3. Automatiserad testpunktshanterare (Test Point Manager) (klicka för större bild)

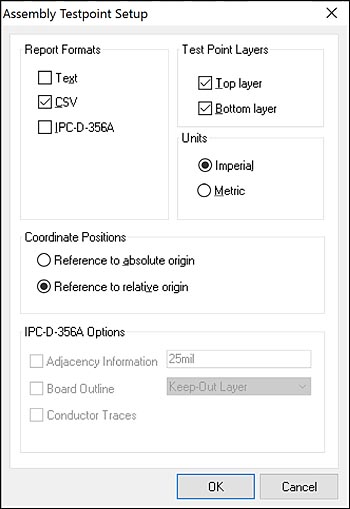

Fig 4. Generering av en testpunktsfil

När designreglerna för testpunkterna väl har konfigurerats kommer EDA-verktyget att automatiskt skapa egenskaper att tillskriva varje testpunkt. Den dokumentation som produceras kommer att vara en testpunktsfil eller -rapport med koordinater för varje testpunkt. Denne rapport kan genereras i ett antal olika filformat, däribland IPC-D-356A. Den kontrakttillverkare som utför testet kan behöva andra filformat, så det är högst rekommendabelt att rådgöra med denne för att verifiera vilka data som krävs för att korrekt kunna utforma testfixturen.

Alternativa (lågkostnads) testmöjligheter

En Flying-Probe-testare kräver inte att man tillverkar någon testfixtur, vilket gör denna metod till den mest kostnadseffektiva lösningen för ICT-test. När man granskar de kontrakttillverkare som skall utföra ICT-test kan det vara lämpligt att fråga dem vilka möjligheter de har till Flying-Probe-testning, som ju bara kräver programmering av testsystemet och inte orsakar några kostnader för att ta fram en testfixtur.

Härtill kommer att om man i efterhand behöver göra några ändringar på testobjektet är man inte låst vid att bibehålla positionen hos testpunkterna. Alla ändringar mellan den gamla och nya versionen kräver endast att man redigerar testprogrammet.

Fig 5. ICT-testsystem med Flying Probe

Angiv tonen under designstadiet

Glöm inte att testfasen av ett färdigt kretskort kan bidraga med upp till 30 procent av den totala designkostnaden, så det är viktigt att utarbeta en sund DFT-strategi för att kunna garantera en sömfri process. Att förstå vilken nivå tillverkarens kunnande och möjligheter ligger på måste vara en av de allra första prioriteterna. Nästa steg är att bestämma hur stor testtäckning som krävs för att kunna garantera en produkt med hög kvalitet som uppfyller alla nödvändiga kriterier.

När planeringsfasen är avslutad ger ett omfattande ICT-test ingenjörerna möjlighet att hitta potentiella fel innan kortet färdigställs för tillverkning. Detta är något som alla designteam och andra intressenter kan ha enorm nytta av. Att implementera denna strategi är ett avgörande viktigt steg för att kunna utveckla en produkt som har lägsta möjliga tillverkningskostnad, samtidigt som man tänker på att bibehålla lägsta felfrekvens och konstruerar med hänsyn tagen till testbarhet.

Chris Carlson, Senior Field Application Engineer, Altium

Filed under: EDA

ICT har av någon anledning (investering i utrustning och fixturer) har hos många hamnat i bakgrunden till förmån för funktionstest, AOI och eventuellt Boundry Scan. Det kan bli en dyr besparing. ICT bör alltid övervägas som teststrategi och inte avfärdas för att det ”är för dyrt”.