Ögondiagram synar FPGA plus dataomvandlare

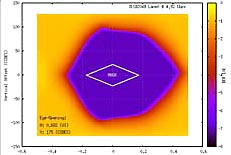

En gratis programvara från Analog Devices åstadkommer ögondiagram för att göra det möjligt att granska signalintegriteten i den seriella länken mellan FPGA och A/D- eller D/A-omvandlare. Sådana kombinationer används exempelvis i radarmatriser eller i mjukvardefinierad radio (SDR).

Att använda ögondiagram är en vanlig metod inom telekom för att analogt granska marginalerna mellan lägena 1 och 0 vid seriell dataöverföring.

Analog Devices presenterar nu en FPGA-baserad referenskonstruktion med programvara och HDL-kod som minskar riskerna i konstruktioner med seriellt förbundna, JESD204B-kompatibla A/D- och D/A-omvandlare.

Verktyget kallas JESD2048 Xilinx tranceiver debugg. Det är anpassat för det seriella datagränssnittet JESD204B som används mellan dataomvandlare och FPGA, med hastigheter från 312,5 Mbit/s till 12,5 Gbit/s och Xilinx SoC-kretsar i serie 7 och Zynq 7000.

Konstruktörer av radarmatriser, software defined radio och andra höghastighetssystem kan med denna ”2-D statistical eyescan” snabbare verifiera signalintegriteten i JESD204B mellan A/D- eller D/A-omvandlare och FPGA som använder gigabit transceivers.

– Medan andra tekniker undersöker signalen innan den har bearbetats av Xilinx automatiska förstärkningskontroll och equalizer-block, ger ADIs metod ett mer korrekt resultat genom att använda Xilinx-transceiverns on-chip eyescan för att göra det möjligt för utvecklare att övervaka signalintegriteten och designmarginalen på deras JESD204B-länkar inuti FPGAn, säger Revathi Narayanan, produktchef för höghastighets-I/O på Xilinx.

ADIs referensdesign samlar in data direkt från on-chip Rx-marginalanalysfunktionen som finns i Xilinx 7-serie och hanterar data lokalt inuti FPGAn eller en av ARMs dubbelkärniga Cortex-A9 MPCore-processorer och visar data på en HDMI-skärm eller över Ethernet på en fjärrövervakningsstation.

Vanligtvis mäter andra verktyg för avsyning utanför chipet, vilket kräver dyr test- och mätutrustning, Eller överförs data tillbaka över JTAG för att visa dem på en värd/utvecklardator i laboratoriet.

Genom att hämta "livedata" kan utrustningens tillstånd övervakas. Alternativa skanningsverktyg mäter vanligtvis höghastighetsdatalänkar genom att generera en pseudo-slumpmässig bitström (pseudo-random bit stream, PRBS) som kontrolleras med avseende på felfrekvens på bitnivå (BER) i en skuten utvecklingsmiljö. Den här metoden beskriver dock inte hur bra konstruktionen fungerar eller om den kan ligga på gränsen till att misslyckas.

ADIs referenskonstruktion mäter däremot länkens stabilitet med hjälp av aktuella JESD204B seriella data som strömmar till FPGAn. Den här användningen av "livedata" gör att signalstabiliteten kan övervakas även efter att konstruktionen har börjat användas på fältet. Det möjliggör realtids- och prediktivt underhåll under produktens livstid.

Dagens referenskonstruktion bygger på Xilinx Zynq-7000 helt programmerbara utvecklings-kit SoC ZC706 och Analog Devices AD-FMCJESDADC1-EBZ FMC-modul. Till dessa krävs en 1080p LCD-monitor och en USB-mus.

Filed under: Utländsk Teknik