Nya forskarrekord på 2013 års IEDM

2013 års IEEE International Electron Devices Meeting i Washington bjöd bland annat på forskningsresultat 16 µm FinFET, MOSFET med nanotråd i kisel och runttäckande gate, monolitisk 3D-arkitektur, p-MOSFET i germanium och visualisering av CBRAM-förbindningar.

IEEE International Electron Devices Meeting (IEDM) har en nästan 60-årig historia. Mer än någonsin är den en av världens viktigaste forum för områdena halvledare, elektroniska komponenter, teknik, konstruktion, tillverkning och modellering där experter från hela världen delger sina senaste forskningsresultat.

Årets konferens, som ägde rum den 12 till 16 december i Washington, bjöd i synnerhet på lösningar för samverkan mellan kretsar och komponenter där allt fler transistorer, specifikationer för komplexa nanometerkonstruktioner och layoutbegränsningar förblir viktiga frågor att utveckla vidare.

Nya ansträngningar fokuserar på att optimera teknologier och kretsar, att analysera effekt i relation till prestanda på en viss yta, att konstruera för tillverkning och processtyrning såväl vad gäller plattformsteknologier för CMOS och dess skalning.

Utveckling och skalning av CMOS

Under konferensen beskrev experter från TSMC tillverkningsprocessen för en 16 nm FinFET. Den betraktas som världsledande inom halvledartekniken.

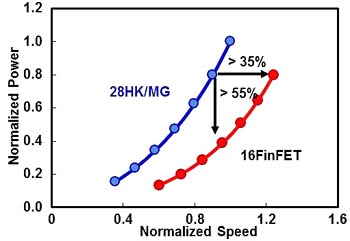

Fig 1. 16 nm-teknik i jämförelse med en 28 nm planarprocess.

Detta är den första integrerade teknologiplattformen under 20 nm nod med speciella egenskaper som 48 nm ”fin pitch” och det minsta SRAM som någonsin har varit inblandat i en integrerad process – ett 128 Mb SRAM med endast 0,07 μm2/bit.

Med avseende på prestanda uppnåddes, förutom dubbla antalet transistorer, en hastighetsförbättring på 35 procent och 55 procents minskning av energiförbrukningen jämfört med TSMCs 28 nm high-k/metallgate planarprocess. Det är i sig en topprestation!

Kortkanaleffekterna, med en DIBL av <30 mV/V ligger mycket väl under kontroll, samtidigt som man anger mättnadsströmmar som 520/525 µA/µm vid 0,75 V (NMOS och PMOS) och en ”off”-ström av 30 pA. Andra speciella funktioner är sju nivåer av mycket komplexa föreningar av koppar/låg-k och plana MIM-element för att begränsa bruset. Fig 1 visar att denna 16 nm FinFET antingen är snabbare eller förbrukar mindre ström i jämförelse med den plana processen.

Toppresterande MOSFET med kisel-nanotrådar

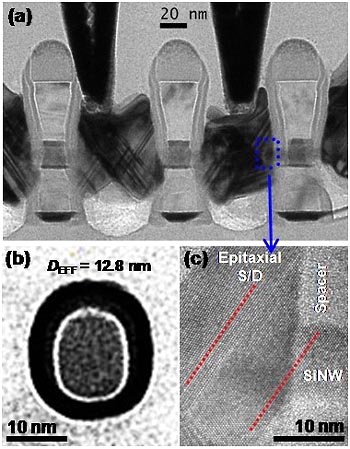

IBM-forskare beskrev en tillverkningsmetod för MOSFET som bygger baserad på kisel-nanotrådar (SiNW). Man har tillverkat GAA-SiNW-element (GAA, Gate All Around ) vars storlekar följer kraven för 10 nm CMOS-teknik.

Ett antal GAA-SiNW MOSFET har producerats. Vissa av dem uppvisar ett delningsavstånd (SiNW-pitch) på bara 30 nm (avståndet mellan nanotrådarna). Avståndet mellan grindens fingrar (gate-pitch) anges till 60 nm.

En MOSFET med 90 nm gate-pitch har redan uppvisat det högsta resultat som någonsin rapporterats för en sådan GAA-SiNW komponent under 100 nm: en topp/medelström på 400 respektive 976 µA/µm vid 1 V. Även om denna forskning är inriktad på n-FET, påpekar forskarna att samma tillverkningsprocess gäller också för p-FET. Det ger potential för en extremt komplex CMOS-teknologi med maximala prestanda. TEM-bilden nedan visar tvärsnittet (a) i en MOSFET, en av nanotrådarna (b) och ett utsnitt (c).

Fig 2. Detaljer av en MOSFET med kisel-nanotrådar.

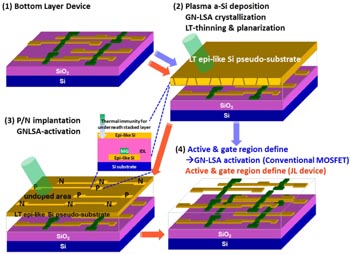

Monolitiska 3D-chip utan TSV

Ett alternativ för skalning är i den vertikala riktningen. Även om 3D-kretsar ofta realiseras genom att stapla separata chips, förbundna med TSVer (Through Silicon Vias) visar vissa TSVer påtagliga nackdelar som att ha relativt stora format och ge parasitkapacitans och termisk missanpassning .

Forskare från National Nano Device Laboratories i Taiwan undvek att använda TSVer och gjorde ett sub 50 nm 3D-chip som integrerar såväl snabb logik som NV-minne och SRAM. De gjorde sin MOS-chip med ultratunn ”body", isolerade med ett 300 nm tunt dielektriskt mellanskikt. För att skapa elementlagren deponerar forskarna amorft kisel som kristalliseras med laserpulser. Sedan följde en mycket speciell CMP-Technology (kemisk-mekanisk planing) vid låg temperatur för att tunna kisel och bana.

Fig 3. Resultatet av processen är extremt tunna och mycket platta komponenter.

Den monolitiska 3D-arkitektur visade mycket intressanta resultat:

* 3 ps logiska kretsar

* 1-transistors 500 ns NV-minne och 6-transistors SRAM med liten yta och låg brusnivå.

Kiselalternativ: snabb Ge p-MOSFET

Germanium (Ge) anses vara ett mycket intressant material för kanalerna i framtida extremt snabba CMOS-komponenter. Orsaken är att germanium ger hög hål-rörlighet vilket leder till snabb switchning. Germanium är instabilt i kontakt med luft. Därför passiveras det med ett silikonskikt. Tyvärr leder det till ökad oxidtjocklek (effective oxide thickness, EOT ) på Ge-skiktet. Det innebär en begränsning för framtida komponenter som måste vara extremt kompakta, med ultratunna oxidlager.

En forskargrupp från universitetet i Tokyo förklarade hur de undvek Si- passiveringslager och istället använde en efter-oxidation med plasmateknik för Ge-kanalens yta och för att optimera gränssnitts egenskaper med source/drain av NiGeSi och ”high-k”-dielektrikat HfO2/Al2O3/GeOx och stackade grindar av Ta. Forskarna upptäckte också att elektronrörligheten kunde höjas i Ge-kanalen till en tidigare ouppnått högt värde med hjälp av en asymmetrisk töjning längs dess kristallyta <110>.

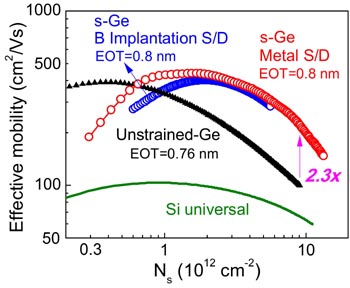

Fig 4. Effektiv rörlighet hos en Ge p- MOSFET.

Med denna teknik byggde de den snabbaste Ge p-MOSFET som någonsin rapporterats, med en rekordsnabb hål-rörlighet av 763 cm2/Vs med ett EOT som bara var 0,82 nm tjock.

Triangulära MOSFETar med InGaAs-kanaler

InGaAs är en lovande kanalmaterial för n-MOSFET med höga prestanda och mycket låg strömförbrukning tack vare dess höga elektronrörlighet. Men för att kunna optimera krävs det en multi-gate-arkitektur som håller bättre kontroll av den elektriska stabiliteten. Dessutom är det svårt att integrera högkristallinskt InGaAs med kisel. Genom att ha flera portar kan man också dra nytta av optimerade kristallytor av materialet för kunna integrera bättre till det.

En japansk forskargrupp, ledd av AIST, gjorde producerade med hjälp av MOVPE (metallorganisk epitaxi i ångfas) triangulära n-MOSFET i InGaAs-på-isolator med släta ytor längs kristallytan <111> med bottenbredder ned till 30 nm.

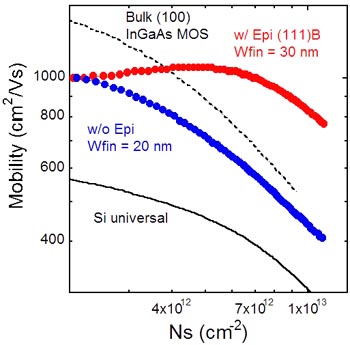

Fig 5. Bilden illustrerar den höga elektronrörligheten hos dessa n-MOSFET.

Enheterna demonstrerades med en grindlängd på 300 nm som gav en framström av 930 µA/µm.

Minsta MLC NAND flashchip

Eftersom flashminnet blir allt mindre och bitledningarna hamnar allt närmare varandra vilket gör att risken för kapacitiv koppling mellan dem ökar avsevärt. Kopplingen kan minska tillförlitligheten i minnet på grund av interferens med data som lagras i respektive minnesceller. Nackdelarna med kapacitiv koppling omöjliggör också aggressiv skalning.

Experter från SK Hynix berättade om det hittills minsta MLC NAND flashminnet (MLC – Multi-Level Cell). Det handlade om ett element i mitten av 1×-noder där ett särskilt plant dike för isolering av luftspaltet används i det aktiva området mellan bitledningarna, medan ordledningarna har standardiserade luftspalt. Luftspalten hos de aktiva bitledningarna minskar även känsligheten för variationer i tröskelspänning. Viktigt är också att den nya lagringstypen har en p-dopad flytande grind gjord av kisel. Det ökar tillförlitligheten i komponenten jämfört med nuvarande MLC NAND flashminne.

Termiskt stabil MTJ-minne för embedded

I MTJ-minnen (magnetisk tunnel junction) sker elektrontunnling genom ett tunt isolerande skikt av ett magnetiskt material till ett annat. På grund av sin snabbhet och sina icke-volatila egenskaper är MTJ-minnet en lovande kandidat för lagring i inbäddade applikationer, men minnenas skalbarhet är problematisk på grund av deras slumpmässiga termiska fluktuationer.

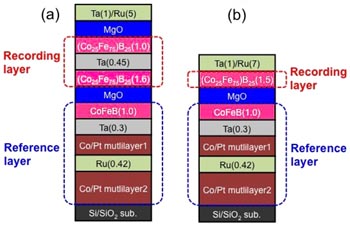

Forskare vid Tohoku University beskrev ett MTJ-minne av CoFeB-MgO med separata skriv/läs-sektioner som är tillverkat i en process med hård mask. De japanska experterna försäkrar att MTJ-minnen kan skalas till 1×-nm noden genom att läslagrets tjocklek kan ökas. Detta leder till en bättre stabilitet mot termiska fluktuationer.

Fig 6. Den separata Skriv/läs-sektionen visas här med (a) dubbelt CoFeB-MgO-gränssnitt och (b) enkelt CoFeB – MgO –gränssnitt.

CBRAM-glödtrådar ses för första gången

CBRAM (Conductive Bridging RAM) är en lovande NV-minnesteknik som ger snabb växling, lågeffektsdrift, långvarig kvarhållning av data och ett mycket bra skalning. Redox-baserade elektrokemi (Reduction-oxidation) av CBRAMs bygger på det faktum att vissa amorfa material med relativt stora mängder av metall beter sig som en fast elektrolyt. Vid förspänning kan metalljoner i sådana isolerande och amorfa skikt bilda ledande trådar, eller förbindningar, genom elektrolyten.

Vid behov kan processen omkastas. Detta motsvarar att skriva eller läsa dataminnen. Komponentens prestanda är direkt relaterade till egenskaperna hos den ledande passagen, men eftersom de är belägna i ett fast skikt är det mycket svårt att "se" vilken gör det svårt att optimera.

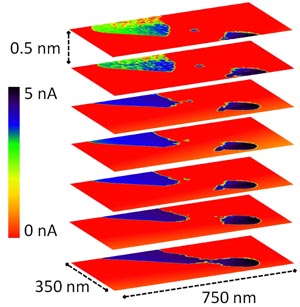

IMEC-forskare beskrev en metod för 3D-avbildning med vilken det är möjligt att använda dessa glödtrådar för att "se" hur och var dessa bildas i det amorfa lagret. Detta liknar datortomografi inom medicinen där man röntgar "skivor" av inre organ och kombinerar dem för att bilda 3D-bilder. IMEC-forskarna använder en atomkraftsmikroskopi (”atomic force microscopy”) för att spela in flera "skivor " av det amorfa skiktet.

Fig 7. En modell av nämnda "skivor". Den blå färgen markerar det ledande området.

Varje skiva kartlägger platser där den elektriska ledning uppträder och alla skivor kombineras sedan för att ge 3D-bilder av hela den ledande glödtråden.

Biosensorer av nanotråd/CMOS

I det växande området för genetisk forskning, är det en mycket svår uppgift att korrekt och kostnadseffektivt upptäcka DNA-molekyler för i elektrolytiska lösningar såsom kroppsvätskor. Eftersom DNA-molekyler är så små och för att det elektriska bakgrundsbruset alltid finns i joniska lösningar, och därmed maskerar närvaron av DNA, är det vanliga sättet att upptäcka DNA-molekyler att märka dem med olika ämnen som kan detekteras med speciella probar. Detta innebär en extra kostnad och komplexitet, vilket skulle kunna undvikas med ett markörfritt direktdetekterande system skulle kunna ha undvikit.

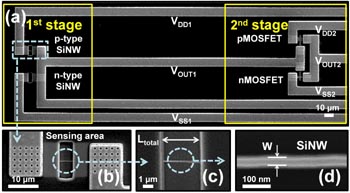

Hittills har det inte funnits någon sådan detektor. Men forskare vid Kookmin University i Sydkorea har på konferensen beskrivit en hybrid-biosensor som för första gången integrerar kiselnanotrådar och CMOS-komponenter för en sådan tillämpning. Den nya biosensorn kombinerar särskilt känsliga nanotrådsytor med lågt brus och läsbarheten hos CMOS-logikkretsar utan markörämnen.

Biosensorn visat en imponerande och konsekvent känslighet, uttryckt som en ändring i utgångsspänning på 1,2 V på grund av en 0,4 förändring i pH-värdet. Med andra ord, en förändring av 1,2 V per 200 femtometer till DNA.

Fig 8. Bilden visar en SEM-bild hybrid-biosensorn med SiNW/CMOS.

SiC IGBT för bättre elnät

Förnärvarande på arbeten med att göra länders elnät "smartare" för att öka deras effektivitet och tillförlitlighet. Styrsystemen i dessa nätverk kräver tillförlitliga och kompakta högspänningsswitchar som klarar >10 kV. IGBT (Insulated Gate Bipolar Transistor) är snabba och effektiva högspänningsbrytare som enkelt kan integreras med vanliga CMOS-kretsar. Om en IGBT var uppbyggd av kiselkarbid (SiC) i stället för vanliga kisel skulle de stå emot de höga linjespänningarna eftersom SiC uppvisar 10 gånger högre spärrspänning än kisel. Problemet är att IGBT-tekniken kräver ett n- skikt på ett skikt av p-typ. Men med SiC är det särskilt svårt att framställa ett bra n-skiktet på p- skiktet.

Forskare vid det japanska institutet för Advanced Industrial Science and Technology (AIST) vände på problemet. De började med ett N++ – substrat och placerade på detta att högkvalitativ n-skikt följt av ett p++ – lager som toppskiktet. Sedan vändes denna trave upp och ner och toppskiktet, bestående av n++ – substrat, avlägsnades. Därmed blir n-skiktet överst och ligger ovanpå p++ – skiktet. Med CMP-teknik kan då ytan polerades och uppbyggnaden IGBT sedan avslutas.

2-kanals 3D-NAND-flash

med snabbare programmering

I de flesta 3D NAND-minnen är alstringen av elektroner, som är primära bärare av elektrisk laddning, mycket snabbare än genereringen av minoritetsladdningsbärare, eller hål, som vanligtvis går i substratet. Denna skillnad förhindrar snabb programmering.

Macronix forskare presenterade i detta ämne ett 2- kanals 3D-NAND-flashminne som integrerar källorna för såväl elektroner som hål i en 3D-struktur med p- och n-kanals drivegenskaper (för source och drain). Forskningen indikerar att det kan vara en annan minnesnod som bildas inom strukturen för ordledningsområdet. Det skulle ge ett mer komplext, 2-kanals 3D-NAND-minne.

Filed under: Halvledarteknik