Minska storlek med partiell omkonfigurering

Ett nytt automatiserat designflöde för Dynamic Function eXchange (DFX) betyder att det nu går enklare och snabbare att spara material- och kretskostnader än någonsin. Funktionen Dynamic Function eXchange (DFX) gör att konstruktörer kan ändra funktionalitet ”i farten” och därmed eliminera behovet av att helt konfigurera om den programmerbara logiken, vilket ytterligare förbättrar den flexibilitet som tillhandahålls av FPGA, Zynq SoC och Versal ACAP-plattformar.

Kunder använder DFX till att minska antalet enheter som krävs i produktionen och upprätthålla ett mindre fotavtryck. Genom att läsa in funktioner som endast krävs vid en viss tidpunkt möjliggör utvecklare en mer effektiv användning av kisel, total effektminskning, förbättrad systemuppgradering och minskade materialkostnader.

DFX passar perfekt för fordonstillämpningar. Vad gäller ADAS-system kan till exempel en enda enhet bearbeta bilder och relaterade sensordata med samma kameror och sensorer för flera körscenarier.

När fordonet är parkerat kan en enda Zynq UltraScale+ MPSoC övervaka fordonets omgivning och identifiera förare som är tillåtna att köra fordonet. Fordonet kan startas när föraren har identifierats. När fordonet har startats initierar detektion av växling från parkerings- till neutralläge en övergång från övervakningsfunktioner för stillastående läge till funktioner för låghastighetskörning, utan att andra nödvändiga funktioner eller enheter påverkas. Övervakningsfunktionerna ersätts genom detta dynamiskt med de körlägesfunktioner som behövs för att bearbeta data från den bakre kameran och andra sensorer vid parkeringsmanövrer i låg hastighet.

En övergång från back- till körväxel aktiverar därefter en övergång från bearbetningsfunktioner för bakgrundsbild och behandling av sensordata till sensorbearbetning av den främre kameran. Dessa ändringar utförs utan behov av återställning eller avstängning av systemet och kan slutföras i tiotals millisekunder.

Partiell omkonfiguration med DFX i aktion

Alla huvudsakliga logik- och dirigeringsresurser i FPGA, inklusive konfigurerbara kretsar med logikblock, DSP-element och block-RAM, kan partiellt omkonfigureras. Med partiell omkonfigurering kan DFX initieras av en signal från externa kretsar eller från systemets huvudsakliga styrenhet, eller från logik, en tillståndsautomat eller en mjuk/hård processor i FPGA, Zynq SoC eller Versal-plattformen.

Låt oss ta FPGA som exempel när vi förklarar hur det här fungerar i praktiken. En maskinvarubaserad styrenhet för partiell omkonfigurering i FPGA tar emot en funktionsförfrågan från tillämpningen och hanterar omkonfigurationen. Detta innefattar att hämta lämplig partiell bitström, leverera den till en intern åtkomstport för konfiguration och koppla bort det dynamiskt omkonfigurerbara logikområdet i syfte att förhindra att omkonfigurationen stör den återstående statiska FPGA-logiken, radera den aktuella funktionen och ersätta den med förkompilerad partiell bitström, initiera den nya funktionen och koppla in logiken på nytt.

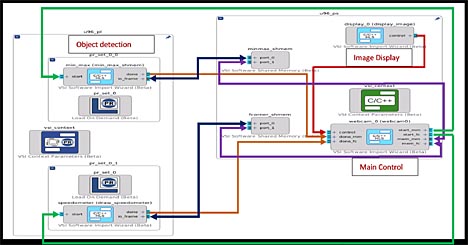

Figur 1 visar hur DFX kan hantera ett användargränssnittsprogram för fordon som ger föraren möjlighet att välja mellan en hastighetsmätare och ett objektdetekteringsöverlägg som visas på en heads-up-display. Av de fyra bearbetningsblocken i det här systemet fångar ”Main Control” in bilden från kameran och skickar data till algoritmen för ”Speedometer Display” eller ”Object Detection”, beroende på förarval. Blocket ”Image Display” visar bilden på skärmen.

Figur 1. Huvudstyrning och bildvisning med dynamiskt omkonfigurerbar objektdetektering och hastighetsmätare (klicka för större bild)

Lämpligt firmware-program hämtas från DDR eller Flash och maskinvaran omprogrammeras om föraren väljer hastighetsmätarfunktionen när ”Speedometer Display” inte är laddad. Styrenheten för konfiguration kan genomföra övergången på endast några tiondels sekunder, vilket gör det möjligt för tillämpningen att växla mellan bearbetning av algoritmer utan att utelämna några data. På så sätt ger partiell omkonfigurering designare möjlighet att välja en mindre och billigare FPGA, spara in på komponentantal och lösningsstorlek samt minimera systemets strömförbrukning.

Konstruktörer kommer att märka att partiell omkonfigurering blir allt mer kraftfull i takt med att fordonselektroniken mäter ökad förfrågan på integrering av nya funktioner och konsolidering av fler och fler funktioner i domänkontrollanter i hela fordonet.

Förutom fordonssystem kan utrustning som medicinska scanners, professionell studioutrustning och bärbar testutrustning dra nytta av samma dynamiska flexibilitet. Den uppvisar även fördelar för försvarstillämpningar. Ett exempel på detta är möjligheten att omkonfigurera funktioner ”i farten”. Förutom detta kan säkerhetsmedvetna enheter använda funktionerna till att uppgradera egen kapacitet genom ta bort och ersätta specifika funktioner.

Bland ytterligare tillämpningar märks kommersiella AI-installationer i samband med att nya neurala nätverksarkitekturer med högre prestanda introduceras. DFX får till följd att AI-acceleratorkort avsevärt minskar genomförandetiden för uppgifter som genomsekvensering genom snabbt utbyte av föråldrade arkitekturer mot toppmoderna neurala nätverk.

Uteslutande funktioner

Den som skapar ett system som utnyttjar DFX måste först identifiera ömsesidigt uteslutande funktioner som kan implementeras i dynamiskt omkonfigurerbar logik. Verktyg som Vivado vägleder användaren genom de nödvändiga stegen. Dessa steg handlar om att definiera den omkonfigurerbara partitionen, skapa och validera planlösningen, definiera förbjudna områden, koppla samman de omkonfigurerbara funktionerna med den statiska FPGA-logiken, infoga avkopplingar på nödvändiga platser och hantera begränsningar i golvplanering på rätt sätt. Den omkonfigurerbara logiken är utformad med hjälp av standardtekniker för placering, anslutningsplanering och tidsstängning.

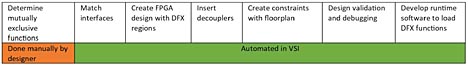

System View, en Xilinx-partner, har skapat Visual System Integrator (VSI), ett verktyg som tillsammans med Vivado automatiserar uppgifter som tidigare utförts manuellt, t.ex. matchning av gränssnitt, infogning av avkoppling, golvplanering och design av dynamiskt omkonfigurerbar logik. Detta förenklar inte bara systemdesignen utan minskar även den typiska tidsåtgången vid genomförande av en DFX-systemdesign. I praktiken kan designflödet komprimeras från veckor eller månader till bara några timmar.

Abstraktion och automatisering

DFX-designprocessen är hierarkisk med hjälp av en syntetisk ”nedifrån och upp”-metod. Omkonfigurerbara moduler syntetiseras oberoende av den oförändrade statiska delen av designen. I VSI-designmiljön kan särskilda ”pr set”-block aktivera DFX. Genom att placera dessa block i samma hierarki som andra bearbetningsblock talar designern om för verktyget att dessa funktioner är ömsesidigt uteslutande och måste köras i samma maskinvaruregion.

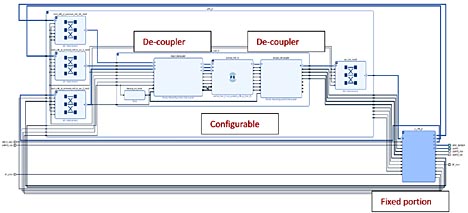

VSI-verktyget abstraherar mycket av komplexiteten i systemdesign med DFX. Verktygen skapar Xilinx Vivado-designen (figur 2) när användaren har beslutat om de funktionella kodblock som är ömsesidigt uteslutande och utser dem i VSI. I den fordonstillämpning som visas i figur 1 innehåller den konfigurerbara delen algoritmer för hastighetsmätaren eller objektdetektering. Den fasta delen av designen fortsätter att exekvera oavsett vilken algoritm som väljs. Avkopplarna isolerar det konfigurerbara området i syfte att skydda den fasta delen under omprogrammeringen.

Figur 2. VSI automatiserar skapande av konfigurerbara funktioner och kretsar för dynamisk övergång (klicka för större bild)

De konfigurerbara områdena måste begränsas till en fördefinierad fysisk region i den programmerbara strukturen så att verktyg för backend, placering och anslutningsplanering kan skapa det partiella firmware-programmet för de olika algoritmerna. Detaljerad information om enheten krävs i regel för skapande av områdesbegränsningar. Men med VSI läser verktyget helt enkelt in enhetsdatabasen och skapar områdesbegränsningarna i designen automatiskt.

Slutligen genererar VSI-verktyget all den support för program- och enhetsdrivrutiner som krävs för att läsa in och läsa om området för partiell omkonfigurering under systemets drift. När huvudstyrningsblocket initierar en läs-/skrivförfrågan i syfte att byta omkonfigurerbart område, avkopplar VSI runtime det omkonfigurerbara området, läser in rätt firmware-program och kopplar in området till resten av FPGA på nytt. Allt detta sker transparent i användartillämpningen.

VSI hanterar även skapandet av den runtime som sitter i Vivado-strukturen i syfte att styra DFX-kommunikationen och hantera isolering och omprogrammering av området. Runtimemodulen har byggts parallellt med designen av utbytbara funktioner och tillhörande FPGA-kretsar, vilket garanterar att runtime är korrekt i designen och redo att användas när FPGA-kretsen är körklar. Figur 3 sammanfattar de uppgifter som VSI automatiserar i syfte att avsevärt påskynda FPGA-design som innehåller dynamiskt omkonfigurerbara funktioner.

Figur 3. VSI automatiserar komplexa och tidskrävande aspekter av DFX-designflödet (klicka för större bild)

Sammanfattning

DFX är en mycket användbar resurs för designers av elektroniska fordonssystem som ställs inför allt mer utmanande krav på att tillhandahålla mer och mer sofistikerade funktioner till allt lägre kostnader, kraft, storlek och vikt. Även flera industri-, handels-, säkerhets- och försvarstillämpningar kan dra nytta av dynamisk omkonfigurering som ger användare extra värde och skyddar mot missbruk.

Willard Tu, Senior Director of Automotive, Xilinx Inc. och Sandeep Dutta, CEO, System View Inc.

Filed under: Fordonselektronik, FPGA