Innovativ SoC-konferens i Vadstena

Den svenska ”system-on-chip”-konferensen SSoCC´14, organiserad av IEEE Sweden Solid-State Circuits/Circuits & Systems Joint Chapter, blev en uppvisning i vad som är möjligt att integrera på kisel och även kiselkarbid.

Vi har tidigare rapporterad om ”Nya lösningar i steget mot kognitiv radio”. Läs mer på https://www.elinor.se/index.php/Teknikartiklar/ om dr Eric Klumperinks idéer för att skapa mottagare med tillräckligt hög dynamik.

Motkopplad LTE-ingång

Det fanns också andra föredrag, väl värda att lyfta fram.

Darius Jakonis berättade om hur man inom Acreo Swedish ICT i Norrköping (Darius Jakonis, Dunkan Platt, Lars Pettersson och Michael Salter, ”Low-power LTE receiver front-end blocks in 28 nm FDSOI CMOS). Projektet är en del av EU-projektet CATRENE. Syftet med det är att utveckla avancerade processmoduler och bidra till två på varandra följande processgenerationers (28 respektive 14 nm) konstruktionsplattformar som bygger på CMOS FDSOI-tekniker (Fully Depleted Silicon On Isulator) för att kunna tillverkas i Europa. Projektet har 10 deltagande organisationer och det leds av STMicroelectronics.

Acreos roll i det hela är att undersöka tänkbara fördelar av CMOS FDSOI i ingångsdelen till mottagare enligt LTE-standarden. Halvledarprocessen är planar, som till skillnad från FINFET, med sin 3D-struktur, kan skalas ned enklare till lägre kostnad och med ökad yield. FDSOI ger potential att snabba upp transistorerna med 30 procent och förbättra verkningsgraden jämfört med motsvarande CMOS i bulk-teknik.

En fördel med FDSOI-tekniken är möjligheten till att förspänna transistorns ”body” för att reducera tröskelspänningen. Därmed kan Vdd minimeras för att sänka effektförbrukningen.

Ett test-chip har tillverkats i 28 nm CMOS FDSOI. Det innehåller bland annat en bredbandig lågbrusförstärkare (LNA) , avstämbar lågbrusförstärkare, kretsar för distribution av lokaloscillatorsignaler och blandare:

* Den avstämbara förstärkaren täcker 0,7 till 2,2 GHz, har 8-15 dB förstärkning och 1,5 dB brustal. För kunna ha hög förstärkning utan instabilitet reduceras millerkapacitansen med en traditionell induktans (i serie med avkopplingskondensator och en Q-värdessänkande resistans) mellan drain och gate. Denna stabiliserade förstärkare kan sedan avstämmas med en varierbar kapacitans i resonans med induktansen (spole eller transformator) mellan matningsspänning och drain.

* Det bredbandiga lågbrussteget täcker 1-40 GHz, har 7 dB förstärkning och brustalet uppskattas till 5 dB. Den låga matningsspänningen, 0,45 till 1 V, begränsar dynamiken: IIP3 anges till 6 dBm.

* Blandaren är en passiv, dubbelbalanserad FET-blandare för 1,9 GHz . Den kräver ingen matningsspänning och drar därför ingen likström. För att minska signalförlusterna förspäns MOSFET-transistorns gate och body-anslutningar. De uppgår till 7,1 dB. IIP3 är +5,8 dBm och IIP2 uppgår till +85 dBm.

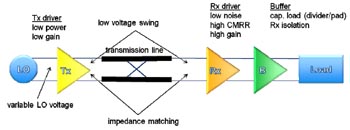

* Distributionen av oscillatorsignalen till olika block har fått en speciell utformning för att minimera effektbehovet. Det kan man göra genom att minska svinget och lägga lämplig förspänning på transitorernas ”body”. Blandaren kräver en differentiellt balanserad signal, vilket för övrig förbättrar signalintegriteten på chipet, liksom överföring på en differentiell transmissionsledning.

Arkitekturen för effektbesparande LO-distribution

Två typer av transmissionsledningar har utvärderats: dels en planar struktur med två parallella ledningar i översta metalliseringslagret, dels en hybridvariant där två lager utnyttjas.

Nästan 2 W PA i 65 nm CMOS

I en annan del i samma projekt undersöks fördelarna med integrerade effektförstärkare i FDSOI-teknik.

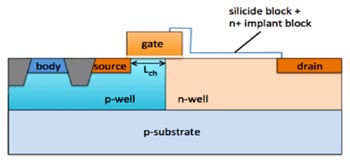

Ted Johansson, adj professor vid Linköpings universitet och tillika värd för SSoCC´14, gav en presentation med rubriken ”Multi-watt PA design in 28 nm FD-SOI CMOS”. Vid effektförstärkarkonstruktion är det en fördel med hög matningsspänning. Men hög spänningstålighet är ett relativt begrepp. Om slutsteget skall integreras i en CMOS-process sätter denna en begränsning som innebär lägre spänningstålighet för varje ny processnod. En skalning till 45 eller 32/28 nm innebär exempelvis att det blir svårt att åstadkomma klass AB-förstärkare för över 2 V matningsspänning. Det beror dels på risken för bristande tillförlitlighet, dels på risken för genombrott mellan komponenter och substratet. En lösning, en LDMOS-struktur i 65 nm CMOS utan extra masker eller processteg presenterades på förra årets konferens (se bilden). Forskarna uppnådde 32,8 dBm (nästan 2 W) i 65 nm CMOS.

LDMOS i 65 nm CMOS

Men FDSOI ger ytterligare fördelar eftersom genombrottet mellan komponenter och substratet är mycket högt. Den lösning som föreslås (T Johansson, Michael Salter, Matteo Vignetti) är att stacka transistorerna. På detta vis kan en konventionell matning på 3,3 V fortfarande användas. För att få tillräckligt hög effekt kan flera stackade steg parallellkopplas. En sådan lösning kan leverera flera Watt i CMOS med nanometermått.

Parallellkopplade, stackade LDMOS på SOI.

Multilevel PWM PA

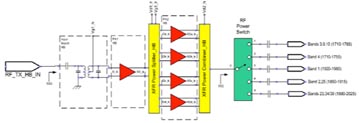

I ett annat föredrag beskrev Muhamad Fahim Ul Haque (”Modified multilevel PWM switch mode power amplifier” av Muhamad Fahim Ul Haque, Ted Johansson och Dake Liu) ett flernivåers pulsbreddsmodulerat switchat slutsteg.

Nyheten ligger just i kombinationen av pulsbreddsmodulerad RF och flernivåers slutsteg som switchas i nollgenomgången med en efterföljande antennavstämning som följer modulationsenvelopen (zero–voltage switching contour based power amplifier with minimum efficiency degradation under back-off).

Principschema för den föreslagna kombinationen.

Den nya kombinationen ger bättre dynamik på höga frekvenser än en renodlad RFPWM, ”radio frequency pulse with modulation”. Dessutom behöver den enbart ett effektslutsteg (PA) och ingen combiner.

Verkningsgraden, om man modulerar med en basbandssignal enligt 802.11g, blir också högre.

Forskartrion visar också att det dynamiska området är konstant om man jämför mellan frekvenserna 3, 4 och 5 GHz, till skillnad från RFPWM vars dynamik minskar med ökad frekvens.

Tidsbaserad A/D

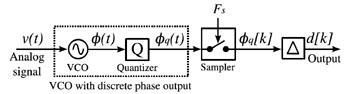

A/D-omvandlare brukar antingen bygga på viktade spänningar eller strömmar. Linköpingsforskarna Vishnu Unnikrishnan och Mark Vesterbacka har i stället föreslagit en lösning som bygger på viktad tid. Fördelen är att lösningen lätt kan implementeras i olika processer med god precision.

Inom detta arbete har man konstruerat en översamplande A/D-omvandlare, byggd enbart på standardceller . Det förenklar syntes och ledningsdragning i ett digitalt konstruktionsflöde.

Den förselagna konstruktionen bygger på första ordningens brusformning där en VCO används för kvantiseringen.

Simuleringar har visat att den förseslagna A/D-omvandlaren i 65 nm CMOS skulle kunna ge 55,5 dB SNDR vid 31,5 MHz bandbredd då 250 MHz samplingsfrekvens används. konstruktionen upptar 0,026 mm2 chipyta och 12,6 mW medeleffekförbrukning, vilket motsvarar en energi av 416 FJ per steg.

Modell av den VCO-baserade A/D-omvandlaren.

Kiselkarbid för höga temperaturer

Vid KTH pågår SSF-stödda HOTSIC-projektet som syftar till att åstadkomma skapa integrerade kretsar i kiselkarbid för att tåla höga temperaturer. Läs mer på https://www.elinor.se/index.php/IC-for-600-grader.html

”Silicon carbide fully-differential amplifier for data acquisition system at high temperature” är titeln på ett ”paper” av YeTian, Ana Rusu och Carl-Mikael Zetterling som Ye Tian presenterade på SSoCC´14. Den beskriver en differentialförstärkare i bipolär teknik på 4H-SiC-substrat.

Kretsen är karakteriserad från 27°C till 500°C. Såväl open-loop-förstärkning som bandbredd ändras med temperaturen: Vid 25 grader är open-loop-förstärkningen 56 dB och bandbredden 2,5 MHz för att sjunka till 39 dB respektive 40 kHz vid 500°C.

För att minska förstärkningsvariationer med temperaturen tillämpas motkoppling.

Förstärkaren har differentiell utgång för att direkt kunna driva en A/D-omvandlare med stort sving och att för begränsa störningar i gemensam mod.

Resultaten visar en god potential för vidare undersökning av analoga kretsar i SiC för höga temperaturer. Det finns en rad applikationer där man behöver betydligt högre temperaturtålighet än med dagens Si-komponenter, t ex inom bilelektronik, flyg- och rymdfart samt bergborrning.

Memristorn – en märklig komponent

Bland de mest udda komponenter som kommit till är memristorn. De bakomliggande teorierna presenterades redan 1971 av Leon Chua. Först år 2008 presenterade Williams vid HP labs en fungerande memristor.

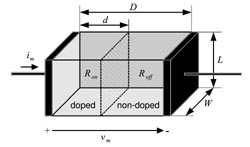

Memristorn är en 2-polig, passiv komponent med minnesfunktion. Den kan beskrivas som två sektioner i serie där den ena är dopad med positiva syrejoner och den andra inte är dopad. Den totala resistansen är en linjär kombination av resistansen hos den dopade och den odopade regionen.

Modell av memristor

Med en ström genom memristorn kan syrejonerna flyttas för att på så sätt ändra resistansen. Den ligger kvar när det inte längre går någon ström genom meristorn, som därmed har en minneseffekt. Avläsningen måste göras, i likhet med dynamiska minnen, med en ”refresh”.

På SSoCC´14 presenterade Joakim Alvbrant, doktorand vid Linköpings universitet, ett arbete (State-transfer-function and bandwith limitation in a non-linear drift memristor model) där han introducerar och analyserar en överföringsfunktion för memristorns tillstånd. Han har bland annat genom simulering funnit en lågpassfunktion över en viss frekvens.

Med utgångspunkt i ekvationerna kan man sluta sig till att memristorn kan användas som amplitudmodulator.

Filed under: Teknikartiklar