Halvledarforskningen i frontlinjen på IEDM

IEDM, IEEE International Electron Devices Meeting, IEDM, har under 60 år varit världens främsta mötesplats för att presentera resultat från den senaste forskningen inom halvledarteknik, konstruktion och tillverkning av elektroniska komponenter, halvledarfysik och skapande av modeller för elektroniska kretsar och komponenter.

Årets föredrag handlar bland annat om CMOS-transistorer i nanometerskala, avancerade minnen, displayer, sensorer, MEMS, nya komponenter i kvantelektronik, empirisk utforskning av fenomen, optoelektronik, effektkomponenter och skördning av energi, höghastighetskomponenter, processteknik, komponentmodeller och simulering.

Konferensen täcker inte bara komponenter i kisel och i sammansatta material från periodiska systemets grupper III och V, utan även nya material, t ex med större bandgap som SiC och GaN, och halvledarkomponenter i organiska material.

Energilagring direkt på chipet

I viss typ av energilagring är kondensatorer att föredra framför batterier: Kondensatorerna försämras inte av tusentals laddningscykler. Det beror på att kondensatorerna är elektrostatiska komponenter och inte, likt batterier, utnyttjar en kemisk reaktion för att lagra energi. Intels forskare ser en potential i att kunna lagra energi i själva chipet. Sådan monolitisk integration skulle kunna appliceras på CMOS-kretsar, sensorer eller energiskördande system som solceller av kisel.

Intelforskarna har studerat elektrokemiska kondensatorer som bygger på nanostrukturer av poröst kisel (P-Si) som täcks av filmer av deponerat atomlager (ALD, Atomic Layer Deposition) av TiN.

Mätningar på täckta P-SI-kondensatorr visar att en hög kapacitans kan åstadkommas: 3 milliFarad/cm2. Detta är inte möjligt att uppnå med icke täckta kondensatorer av poröst kisel.

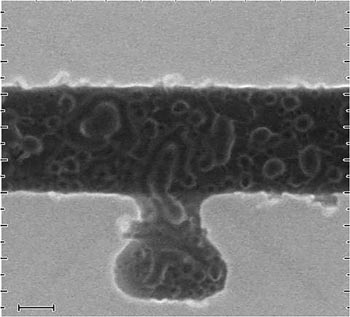

Bilden av den porösa strukturen är tagen med svepelektronmikroskop (SEM).

Den porösa strukturen på bilden ovan illustrerar den verikalt avsmalnande nanostrukturen. Den åstadkoms tack vare olika etsförutsättningar, påverkade av strömintensiteten.

De kondensatorer av TiN-täckt poröst kisel som forskarna har byggt har uppvisat stabila kapacitansvärden även efter 1000 cykler vid 50 mV/s.

En DSP bakom varje pixel

Hittills har det varit svårt att åstadkomma bildsensorer som samtidigt har hög upplösning med snabb bildhastighet. NHK-forskare har utvecklat en 3D-uppbyggnad där det finns en DSP bakom varje pixel.

Traditionell ligger fotodetektorerna och DSP i samma plan på substratet. En DSP tar hand om flera fotodetektorsignaler genom tidsdelning. Detta sänker bildhastigheten. Men tack vare en tredimensionell uppbyggnad blir det möjligt att ha en DSP under varje pixel för att undvika en kompromiss mellan bildupplösning och bildhastighet.

3D-stackade bildsensorer har det rapporterats om tidigare, men de har inte haft en DSP under varje pixel, eller har det utnyttjat TSV-förbindningar( Through-Silicon Vias) eller mikrokulor (”micro bumps”) vilket har minskat upplösningen.

NHK-forskarna diskuterar under IEDM hur fotodioder och inverter-lager förbinds med inlagda guldelektroder för att kunna A/D-omvandla varje pixelsignal till en utmatad pulsfrekvens.

Så här ser den schematiska uppbyggnaden ut.

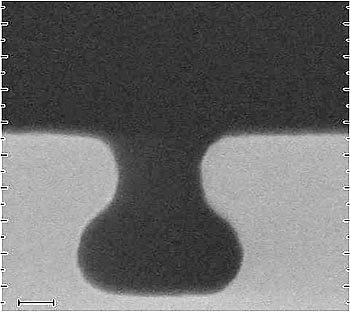

Och så här ser ett tvärsnitt ut av en förbunden CMOS sensor-pixel, tagen med ett elektronmikroskop.

Inga ”voids” (oönskade hålrum) kunde observeras hos förbindningarna. Det övre lagret tunnades ned till 6,5 µm.

En prototypsensor med 64 pixlar har byggts upp med gott resultat. Dynamiken uppgick till över 80 dB och forskarna tror att det finns en potential för att kunna nå 100 dB.

Varje fotosensor, stackad över en inverter, mäter 60×60 µm.

3D-stackning

Thohoko universitet har utvecklat en TSV-teknik (Through-Silicon Vias) som skall passa särskilt väl för självgående fordon. I det sammanhanget krävs ett intelligent system som mycket snabbt samtidigt kan ta hand om flera olika typer av data.

Denna röntgentomografi visar en TSV-förbindningar av fyra lagers kisel: Till vänster fyra stackade CPUer och till höger två stackade minnen.

Med en tredimensionell uppbyggnad blir det möjligt att ställa samman funktionsblock som processorer, minnen, sensorer, logik, analoga funktioner, fotonik och effektkretsar i ett gemensamt chip.

Forskarna vid Thohoko universitet ligger i framkanten och har tidigare visat upp 3D-stackning i snabba bildsensorer. På IEDM visar de hur man kan ha fyra stackade processorer intill två stackade cacheminnen på en bärare av kisel i en rekonfigurerbar, 3D-integrerad konstruktion som utnyttjar TSVer.

För att genomföra projektet krävdes det boundary scan, inbyggt självtest och självreparerande funktioner.

Ultrasnabbt tack vare 3D

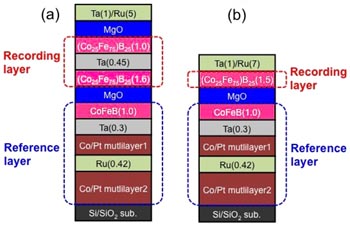

I ett annat föredrag presenterade T Hanyo m fl från Thoku universitet en icke flyktig teknik för logik i minne.

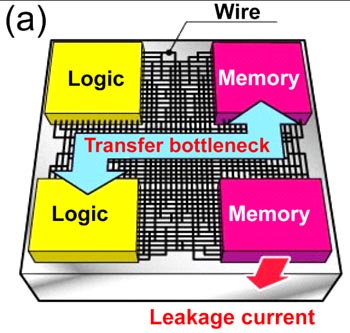

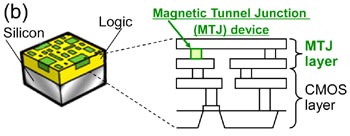

Så här ser idag en krets med minnen och teknik ut.

I ett konventionellt chip med kombinationen logik och minne sker förbindningarna globalt. Över dessa förbindningar skyfflas data. Längden hos dessa förbindningar begränsar snabbheten samtidigt som det icke flyktiga minne kontinuerligt förbrukar ”standby”-effekt.

Från Tohoku ser förslaget i stället ut såhär.

Tohokuforskarna diskuterar i stället att använda en tredimensionell struktur där man använder icke-flyktiga magnetiska tunnelöverföringar (Magnetic Tunnel Junctions, MTJ) som minneselement för att förbättra hastighet och tillförlitlighet i storskaliga CMOS-kretsar och samtidigt spara effekt. MTJer är mycket snabba och icke-flyktiga minneselement. Dessa är tredimensionell integrerade med logik.

Denna teknik, som man benämner ”nonvolatile logic-in-memory”, demonstreras på IEDM genom bygget av en FPGA, ett ternärt CAM-minne (TCAM) och en microcontroller.

Tack vare att man kunde undvika långa förbindningsledningar i kombination med de snabb MTJ-cellerna har man åstadkommit en teknik som snabbar för ultrasnabba, ultraströmsnåla tillämpningar.

Nanotrådsgate på plast

De minnen som hittills utvecklas för flexibla substrat har haft stora detaljer och levererat måttliga prestanda jämfört med vad som kan göras på kiselwafers. Orsaken är begränsningar i materialen och begränsningar i tillverkningsmetoderna.

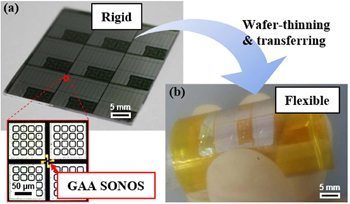

J M Choi m fl från KAIST berättar på IEDM hur man kommit förbi dessa begränsningar genom att lägga ”single crystal silicon nanowire gate-all-around (GAA) SONOS”-minneskretsar på plastsusbtrat.

GAA SONOS FET på en SOI-wafer. Fotot demonstrerar böjbarheten.

Minneskomponenternas raderingshastigheter, återhämtning och långtidsegenskaper (>10 000 programmerings/raderingscykler) var desamma som innan de lades på plastsubstratet. Dessutom bestod deras elektriska egenskaper då substratet böjdes. Det skapar en möjlighet till att skapa högpresterande böjbara produkter.

Överföringsprocessen inleds med att ett skyddslager läggs på GAA SONOS-komponenten. Därpå läggs den tillfälligt på en wafer för att kunna hanteras. Baksidan tunnas av till dess att de gömda oxidlagret träder fram (Buried Oxid, BOX). BOX-lagret fungerar som ett lager som stoppar etsning av kisel. Den ultratunna (~1 µm) film som återstår består av kretsar av GAA SONOS är överförda överförs till en flexibel film. Därefter tas den temporära wafern liksom skyddslagret bort.

Processflödet och ett foto av den ultratunna GAA SONOS-komponenten överförd till ett flexibelt substrat.

Tvåkanals nanotrådtransistor

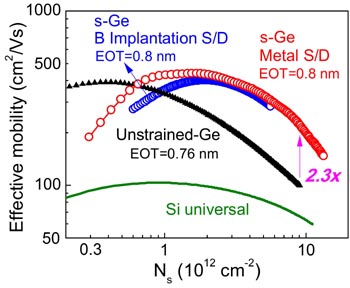

FDSOI, Fully Depleted Silicon On Isulator, innebär att transistorns kanal ligger på ett extremt tunt isolatorlager. Tack vare det tunna isolatorskiktet kan utarmningsytan täcka hela kanalen. Därför behöver inte kanalen dopas. Jämfört med en MOSFET på ”bulk” ger en FDSOI mycket bättre elektrostatiska karakteristika. Det gömda oxidlagret (”buried oxide layer”) minskar parasitkapacitanser och läckström mellan source och drain.

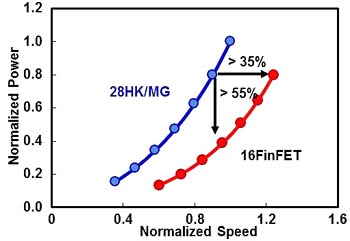

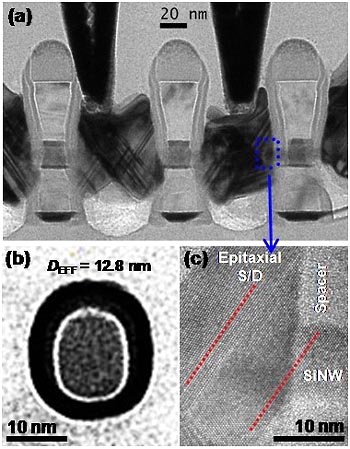

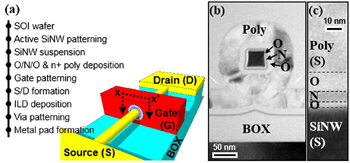

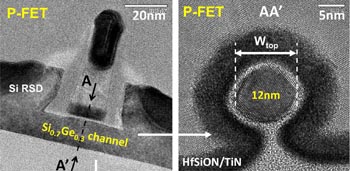

I ett föredrag från CEA-LETI beskriver P Nguyen, m fl, en integration av en Si NFET och en PFET i uttöjt SiGe i en arkitektur som inbegriper nanotrådar. Gatelängden är 15 nm.

Denna tvåkanals nanotrådtransistor ses som en lovande väg för att skala ned med än vad som är möjligt med FinFET eller FDSOI.

Komponentens PFETar har en gate vars SiGe är utsträckt med en profil likt den grekiska bokstaven omega. Detta ger en god kontroll av elektrostatiska fält i kanalen.

Profilen av gaten bildar ett omega

Dessa PFETar är samintegrerade med NFET i en helt CMOS-kompatibel SOI-process.

Gatelängden är skalad till 15 nm och nanotrådarna har 7 nm diameter.

I testkretsar har en 80 stegs ringoscillator byggts med lovande resultat. Resultaten visar att fördröjningstiden är 50 procent kortare än i motsvarigheter i kisel.

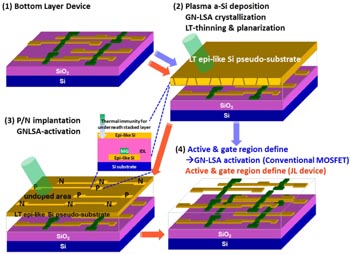

FDSOI för 10 nm

Q Liu och hans forskarteam inom alliansen ST Microelectronics/IBM Technology Development hävdar i sin presentation att FDSOI kan tillverkas i en konventionell lågkostnads halvledarprocess till skillnad från mera komplexa FinFET-arkitekturer.

Dessa forskare har med framgång lyckats implementera FDSOI med töjt kisel i 10 nm processnod, med allt vad det innebär i fråga om gate-längder och dimensioner hos ett gömt oxidskikt (”buried oxide”, BOX).

Två saker rapporteras som har gjort det möjligt att skala ned FDSOI till 10 nm nod: Dels en avancerad teknik för att töja kisel, dels minskad BOX-tjocklek.

Forskarna rapporterar också att de har lyckats demonstrera ”strain reversal” genom att lägga in SiGe i en kortkanals PFET.

Beträffande prestanda uppnådde komponenterna vid 0,75 V en effektiv drivström på 340 µA/µm för en NFET med Ioff =1 nA/µm.

Med en kompressivt uttöjd 30 procentig SiGe-on-isolator-kanal (SGOI) på 20 nm tunt BOX-lager är den effektiva drivströmmen för en PFET 260 µA/µm vid Ioff = 1 nA/µm.

Kondensationstemperaturen visade sig ha stor inverkan på kanalkvaliteten. En lågtemperatursprocess utvecklades för att forma en felfri SiGe-kanal av det uttöjda SOI-substrat som man utgick ifrån. I de två bilderna nedan ser man, med hjälp av ett svepelektronmikroskop, resultaten av en högtemperaturprocess, respektive en lågtemperaturprocess.

Detta klena resultat fås med en högtemperaturprocess.

Lågtemperaturprocessen ger ett felfritt resultat.

TRAM bättre än PRAM

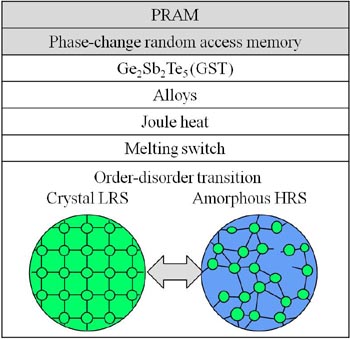

Fasskiftande minnen, PRAM, ”Phase-change Random Access Memories”, är en teknik för icke flyktiga minnen som bygger på en snabb upphettning av kalkogena material som skiftar mellan kristallinska och amorfa tillstånd. De två tillstånden ger olika resistans, vilka representerar 0 och 1.

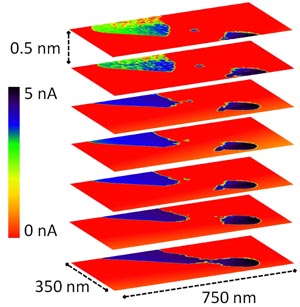

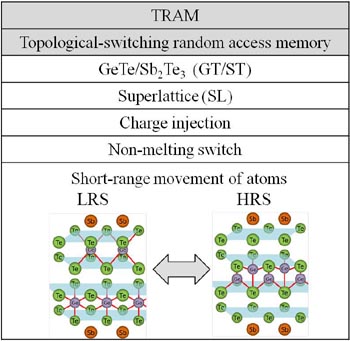

Det japanska forskningsprojektet LEAP (”Low-Power Electronics Association and Project”), som letts av N Takaura, har utmynnat i ett nytt slags minne, kallat TRAM, ”Topological-switching Random Access Memory”.

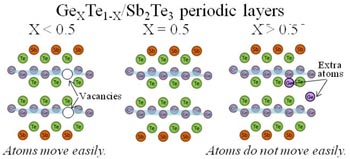

Lagringen av data bygger på att Ge-atomer flyttas inom ett kristalliniskt suppergitter av GeTe/Sb2Te3. Energin för att programmera ett TRAM är betydligt lägre (en tjugondel) än för ett PRAM.

De minneskretsar av typen TRAM som forskarna har byggt upp arbetar med en set/reset-ström så låg som 55 µA, vilket är det lägsta värdet för extremt kompakta minnen.

Mad elektronmikroskop har man lyckats se sekvenserna för Ge-Te och Sb-Te i supergittret. Med detta kunde forskarna förstå retensionstid och uthålligheten i TRAM. De tog också fram supergitter med 6 nm tjocka Sb2Te3-lager och andra ämnen med sammansatta bottenlager får att förstå elektriska karakteristika för TRAM.

Här visas de viktigaste egenskaperna för ett PRAM.

Ett TRAM har helt andraegenskaper än PRAM.

Bilden visar en modell av atomrörelserna i TRAM.

Resistivt RAM

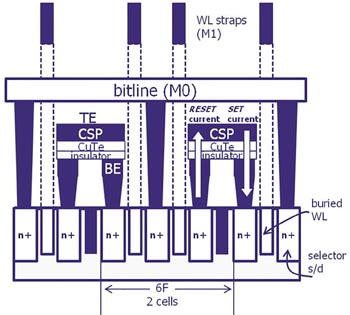

En lovande kandidat för framtidens icke-flyktiga minnen är ett ReRAM, ”Resistive RAM”. I 27 nm processmod har Micron Technology tillverkat ett 16 Gb ReRAM-chip med kopparfiler och en cellstorlek av 6F2. Detta chip uppvisade 133 MB/s skrivhastighet och 666 MB/s läshastighet.

Enstaka ReRAM-celler har visats tidigare, men detta är den första massproducerbara integrerade krets som demonstreras. Cellstrukturen innebär en transistor per cell, en modifierad RAM-struktur och en självlinjerande kontaktering som alltså inte kräver någon litografi.

Den principiella uppbyggnaden för Microns ReRAM.

Filed under: Halvledarteknik