Genombrott för ny III-V FinFET-process

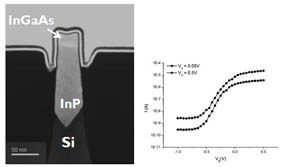

Forskningscentret imec meddelar att man framgångsrikt har demonstrerat världens första III–V FinFET-kretsar, monolitiskt integrerade på 300mm kiselskivor, genom en unik process där kisel-”fins” ersätts.

Bedriften visar på framsteg mot 300mm och framtida 450mm waferproduktion i stora volymer med avancerade heterogena CMOS-kretsar, monolitiskt integrerade halvledarföreningar, på kisel med hög densitet. Enligt imec möjliggör genombrottet en kontinuerlig CMOS-skalning ner till 7nm och därunder men också nya möjligheter till heterogena system med hybrid CMOS-RF och CMOS-optoelektronik.

– Vad vi vet är detta världens första fungerande CMOS-kompatibla III-V FinFET-krets, processad på 300mm wafers, säger An Steegen , senior vice president core CMOS på imec. Det här är en spännande prestation som visar på ett livskraftigt alternativ för nästa generations ”state-of-the-art” kiselbaserad FinFET-teknik för produktion i höga volymer.

Spridningen av smarta mobila enheter och de ständigt växande förväntningarna på bandbredd och uppkopplingsmöjligheter kommer att driva på det ständiga behovet av framsteg inom både mjukvara och hårdvara, som sträcker sig från nätverk och dataservrar till mobila prylar. Kärnan för hårdvaran blir nya processteknologier som möjliggör än mer strömeffektiva CMOS-transistorer och ökad integration, vilket ger möjlighet till en högre grad av funktionalitet. Det här skyndar på processtekniker som ger möjligheter till heterogena kretsar som kan maximera systemets prestanda.

– Under det senaste decenniet har skalningen av transistorns storlek präglats av flera språng i processteknik för att uppnå prestanda- och effektförbättringar. Ersättningen av poly-silicon gate med en high-k metal-grind i 45nm CMOS-teknik 2007 utgjorde en flektion mot att integrera nya material i transistorn. Möjligheten att kombinera skalade icke-kisel och kisel kretsar kan bli den nästa dramatiska lyftet för transistorn och bryta nästan 50 år av kiselregim över digital CMOS. Det här arbetet utgör ett viktigt steg för att möjliggöra denna nya paradigm, säger Aaron Thean , chef för logic R&D vid imec.

Att kombinera olika material och strukturer i heterogena transistorer med hög densitet har ifrågasatts med avseende på om det är möjligt att samtidigt uppnå en låg komplexitet och felfrihet. I imecs nya process, som beskrivs som ett genombrott, ersätts kisel-”fins” med indium galliumarsenid (InGaAs) och indiumfosfid (InP), och då uppnått en nästan åttaprocentig missanpassning i gitterkonstanten. Den nya tekniken bygger på ”aspect ratio trapping” av kristalldefekter, ”trenchtrukturer” och innovationer för epitaxiella processer.

Imecs forskning om nästa generations FinFETs utförs som en del av institutets core CMOS -program , i samarbete med imecs nyckelpartners: såsom Intel , Samsung , TSMC , Globalfoundries , Micron , SK Hynix , Toshiba , Panasonic , Sony , Qualcomm , Altera , Fujitsu , nVidia , och Xilinx.

Filed under: Utländsk Teknik