Fyra 64 bits ARM-kärnor i nästa FPGA-generation

Altera tar inte bara steget från 32 till 64 bit i sin kommande Stratix 10 SoC. Med fyra 64-bits ARM Cortex-A53-kärnor och upp till 10 TFlops DSP-prestanda kvalar den nya FPGA-familjen in som nästan vad som helst. Och med en ordentlig satsning på OpenCL finns det möjligheter att göra utvecklingsarbetet enklare.

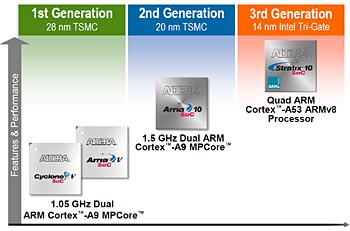

Altera presenterade tidigare i år en hel del av innehållet i den kommande toppfamiljen Stratix 10 SoC. Det skulle bli den första FPGA-generationen att tillverkas hos Intel i deras 14 nm Tri-Gate-process och redan då stod det klart att man tänkte öka antalet hårda block kraftigt. Men inte förrän nu har man velat berätta vilken kraftig satsning som görs på processorsidan.

– Hittills har vi satsat på relativt enkla processorsubsystem i mellanklasskomponenterna, men när vi nu lägger in processorer också i toppmodellerna tar vi ett ordentligt steg uppåt, säger Danny Biran, Senior Vice President, Corporate Strategy and Marketing.

– Vi räknar med att öka processorprestanda med minst sex gånger, jämfört med våra hittills snabbaste subsystem. Det gör vi på flera sätt. De nya 64-bits Cortex-A53-kärnorna är betydligt effektivare än de tidigare och de kommer också att ha en högre maximal klockfrekvens. Dessutom dubblar vi antalet processorkärnor, från två till fyra.

– Ändå behåller vi bakåtkompatibilitet med våra andra processorbaserade komponenter. Cortex-A53-kärnorna har en inbyggd 32-bits kompatibilitetsmod som går att använda i de fall där man måste kunna använda identiskt samma programvara.

Danny Biran, Senior Vice President, Corporate Strategy and Marketing, Altera

Heterogena system

– Allt det här är en del av vår satsning på det som vi brukar kalla "silicon convergence", men som ute i industrin brukar kallas "heterogeneous computing". Grundidén är att olika typer av byggsystem, ASIC, FPGA, DSP och mikroprocessorer, erbjuder olika nivåer av flexibilitet, programmerbarhet och effektivitet. Här mäter vi effektiviteten i termer av prestanda i förhållande till energiförbrukning.

– Problemet för användarna är att de sällan kan göra ett totalt val mellan effektivitet och flexibilitet. De behöver bådadera och det gör att de kräver system som innehåller flera olika teknologier som kan arbeta tillsammans.

– Skillnaden mellan oss och de andra är att vi kan kombinera alla befintliga teknologier med programmerbar logik. Det gör oss unika. Vi kan kombinera programmerbar logik som klockas över 1 GHZ med mycket kraftfull flyttals-DSP och mycket kraftfulla mikroprocessorer. När vi kombinerar det här med ett konstruktionsflöde baserat på OpenCL får vi ett sammanhängande och ytterst kapabelt system.

Enklare utveckling

OpenCL är en öppen standard för heterogena system och Altera är ett av de företag som satsar hårt på standarden. Tanken är att göra det lättare att använda processorbaserade FPGA-kretsar, vilket blir allt viktigare i takt med att man lanserar nya kombinationsfamiljer. Idag finns hårda processorkärnor i allt från Cyclone V SoC, över Arria V och 10 SoC och snart hela vägen upp till Stratix 10 SoC.

– Vi presenterade nyligen en SDK för OpenCL och vi har ett nära samarbete med ARM på verktygssidan, speciellt vad gäller debugverktygen. Vi har till exempel integrerat debugverktygen från ARM så att man kan sätta brytpunkter på processorerna och se vad som händer på FPGA-sidan och vice versa.

Nya tillämpningar

Att hålla kommunikationen på chipnivå mellan processorer, signalprocessorer och programmerbar logik ger naturligtvis en rad fördelar. Det blir betydligt energieffektivare och man behöver inte tappa prestanda i kommunikationen mellan komponenter. Med Stratix 10 SoC kommer den här typen av funktioner också för de allra mest kraftfulla komponenterna och det öppnar en del nya dörrar.

– Vi ser till exempel hur Stratix 10 SoC kan användas i datacenter. FPGA-logiken är perfekt för att accelerera sökmaskiner och inspektera datapaket i hög hastighet. DSP-funktionerna passar utmärkt för matrismanipulationer och flyttalsberäkningar, medan de snabba 64-bits-processorerna tar hand om flödeskontroll, lastbalansering, energihantering och hantering av FPGA-länkar. Processorerna är också värdar för OpenCL. Totalt sett kan man nå prestandaökningar som annars vore omöjliga.

Kombinationen av snabba processorer, signalprocessorer och FPGA-logik ger fördelar också i många andra tillämpningar. Det gäller till exempel nätverk och dataöverföring, militära tillämpningar, bland annat radarapplikationer, och mycket annat.

– I nätverkstillämpningar är inte behovet av signalprocessor lika stort, därför finns versioner med mindre mängd DSP. Men i till exempel radartillämpningar är DSP-behovet mycket stort.

Kommer vi då att få se den här typen av kombinationskomponenter ta över helt på de konventionella FPGA-komponenternas bekostnad?

– Utvecklingen mot heterogena system går mycket snabbt och jag tror knappast att vi i framtiden kommer att se avancerade FPGA-familjer helt utan processorer. Det innebär i och för sig inte att alla varianter inom en familj måste innehålla processorer, men det vanligaste kommer säkert att vara kombinationskretsar av den här typen.

Altera har kommit såpass långt med Stratix 10 att man räknar med att ha fungerande testchip före nyår. Mjukvaran skall vara klar att använda i början av nästa år och Altera räknar med att ha riktiga Stratix 10 SoC-komponenter framåt fjärde kvartalet nästa år.

ARM-baserade processorsubsystem finns eller kommer att finnas i de flesta av Alteras FPGA-familjer

Filed under: FPGA