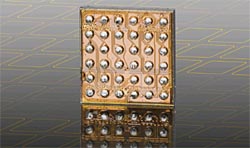

Fler videoblock för FPGA

Från Lattice kommer sju nya videobaserade IP-block för företagets FPGA-komponenter i CrossLink-serien. Blocken gör det lättare att skapa bryggor mellan olika standarder.

– Våra kunder frågar efter FPGA-kretsar med MIPI D-PHY-kapacitet för att klara gränssnittsproblem, säger Tom Watzka, product marketing manager hos Lattice Semiconductor. Men alltför ofta stöter de på problem när det gäller energieffektivitet, storlek eller prestanda. De nya IP–kärnorna gör det betydligt lättare att snabbt nå resultat.

CrossLink-serien lanserades förra året som en lösning på dagens allt komplexare videoapplikationer. Komponenterna klarar avancerade videotillämpningar med låg energiförbrukning för till exempel fordonssystem och drönare. De nya IP-block som nu lanseras är:

* CSI-2/DSI D-PHY Receiver – konverterar MIPI CSI-2/DSI-dataströmmar till parallella data.

* CSI-2/DSI D-PHY Transmitter – konverterar parallella dataströmmar till MIPI CSI-2/DSI.

* FPD-LINK Receiver – konverterar FPD-LINK-videoströmmar till ”pixel clock domain”.

* FPD-LINK Transmitter – konverterar pixeldataströmmar till en FPD-LINK-videoström.

* SubLVDS Image Sensor Receiver – konverterar SubLVDS-videoströmmar från bildsensorer till ”pixel clock domain”.

* Pixel to Byte Converter – konverterar data i pixelformat till parallella byteformat för D-PHY-sändare.

* Byte to Pixel Converter – konverterar parallela byteformat från en D-PHY-mottagare till pixelformat.

Dessutom finns en ”1:2 MIPI DSI Display Interface Bandwidth Reducer”, som använder några av IP-blocken för att konvertera en videoström till två, eller till en videoström med lägre upplösning.

Filed under: Utländsk Teknik