Effektiv ISO 26262-komplians för fordonschip

Chip och integrerade kretsar för fordonstillämpningar bildar ryggraden i avancerade system för förarassistans (ADAS) och kommunicerande, självkörande fordon (CAV). Även om integrerade kretsar är mycket tillförlitliga och har lång livslängd kan det ändå uppstå fel i dem. Fysikaliska fenomen som elektromigrering kan exempelvis orsaka avbrott och kortslutningar som permanent skadar kretsen. Alfapartiklar i kosmisk strålning kan träffa en krets och förändra innehållet i minnet. Sådana händelser kan orsaka felaktiga funktioner som t.o.m. kan leda till förlust av människoliv. Jörg Grosse och Sergio Marchese, OneSpin Solutions går här in på FMEDA-automation och felanalys i säkerhetsmekanismer. Varför är detta viktigt, och hur kan det åstadkommas mer effektivt?

Toyotas problem med oavsiktlig acceleration gav en olycklig demonstration av hur fel i elektroniken kan ge upphov till trafikolyckor. En avancerad undersökning har kommit fram till att ett av de kritiska problemen hos de inblandade Toyota-modellerna hade att göra med felkorrigeringsfunktionen – eller frånvaron av en sådan – i IC-kretsarnas minne. Dessutom visade undersökningen att i stora fordonsflottor inträffar farliga fel nästan dagligen.

Jämfört med de chip som användes i Toshiba-fallet är dagens integrerade kretsar flera storleksordningar mer komplexa. Till och med fordon i mellanklassen har funktioner långt utöver automatisk acceleration och bromsning, som exempelvis automatisk styrning (assistent för filhållning). Ständigt minskande transistorstorlekar och ökade krav på låg effektförbrukning har medfört att det krävs allt lägre energi för att ändra tillståndet hos en krets, vilket gör den mer sårbar.

För att skydda mot eller kontrollera fel har moderna integrerade kretsar för fordonsbruk ett antal olika funktioner som kallas för säkerhetsmekanismer (SM). Speciellt för skydd av minnet innehåller många ofta använda SM speciella moduler för felkorrigerande kod (ECC) som korrigerar enkelfel och detekterar dubbelfel (SECDED), eller t.o.m. korrigerar dubbelfel och detekterar trippelfel (DECTED).

Att mäta chipsäkerhet

ISO 26262, som är den funktionella säkerhetsstandarden för elektroniksystem i vägfordon, definierar viktiga mätetal och mål för fyra integritetsnivåer av fordonssäkerhet (ASIL-A, ASIL-B, ASIL-C och ASIL-D). En IC som kontrollerar bakljusen kräver en lägre integritetsnivå (troligen ASIL-A) än en IC som kontrollerar styrningen (troligen ASIL-D). Ingenjörer som utvecklar fordonselektronik måste implementera SM-mekanismer och uppvisa evidens enligt den hävdade ASIL-nivån.

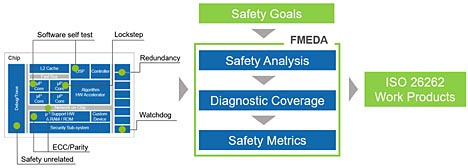

FMEDA (felmoder, effekter och diagnostisk analys) är en etablerad, systematisk process för att utföra kvantitativa analyser av felmoder och diagnostiska funktioner hos en integrerad krets (se Fig. 1), Detta är en tidkrävande och kostsam uppgift, även för mål enligt ASIL-B.

Fig 1. FMEDA-processen har tre viktiga steg: (1) Analys av säkerhetsarkitekturen. (2) Bestämning av den diagnostiska täckningsgraden. (3) Beräkning av säkerhetsmätetal enligt ISO 26262. (klicka för större bild)

FMEDA-processen har tre kritiska steg: 1. Validering av kretsens säkerhetsarktiektur samt uppdelning av hårdvarufunktioner och -fel enligt felmoder. 2. Bestämmande av den diagnostiska täckningsgraden, som mäter förmågan hos säkerhetsmekanismerna att garantera att säkerhetsmålen uppfylls. 3. Beräkning av säkerhetsmätetalen för hårdvaran enligt ISO 26262.

De kritiska felmätetalen i ISO 26262 är SPFM (mätetalet för enpunktsfel), LFM (mätetalet för latenta fel) och PMHF (sannolikhetsmätetalet för sumpmässiga hårdvarufel). Enpunkts och residuella fel orsakar brott mot säkerhetsmålen. Avsikten med att använda SM är att minska antalet residuella fel så att den önskade SPFM-nivån uppnås. Latenta fel orsakar å andra sidan inte själva några brott mot säkerhetsmålen, men kan göra det om ytterligare fel uppstår. Latenta fel kallas också för multipunktsfel (av ordningen två). Ett fel som påverkar en SM skulle t.ex. kunna kvarstå latent, och påverka dennas funktion. Ett andra fel, som skulle kunna uppstå långt senare och som man förutsett skulle detekteras och indikeras av en skadade SM, kan missas och leda till farliga fel i kretsens funktion.

Det är värt att notera att fel i SM också kan vara residuella. Detta är ett olyckligt scenario där ett fel i en skyddsfunktion kan leda till fel på den integrerade kretsen. Visserligen borde det uppstå proportionellt få sådan fel, annars skulle ju en SM kunna förvärra situationen snarare än förbättra den. Men bara en omfattande analys kan bekräfta detta.

Suboptimala FMEDA-flöden bygger på ofta felbehäftade och arbetsintensiva manuella analyser av säkerhetsarkitekturen. Dessutom använder verifierings- och säkerhetsingenjörerna ofta omfattande felsimulering för att bestämma säkerhetsmätetalen.

Felsimuleringen har tre kritiska brister: För det första kan den bara ge stimulusberoende mätetal. Detta påverkar förtroendet för giltigheten av resultaten, speciellt för säkerhetselement som ligger utanför kontexten (SEooC). För det andra krävs tillgång till avsevärda beräkningsresurser. För det tredje går det åt avsevärda ingenjörsresurser för att sätta upp utrustningen, analysera resultaten samt förbättra kvaliteten på stimuli. Däremot är felklassificering baserad på formella metoder mer noggrann och kräver inte heller några stimuli. Men det kan uppstå komplexitetsproblem som begränsar dess användbarhet.

Säkerhetscentrerad partitionering av hårdvaran

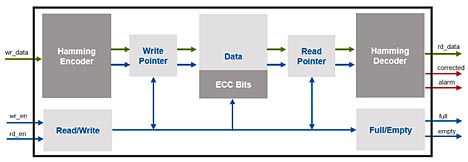

Renesas Electronics och OneSpin Solutions presenterade vid konferensen 2019 DVCon Europe i München en artikel (se Fig 2) där författarna introducerar en automatiserad, effektiv och skalbar FMEDA-process för digitala kretsar. Resultat som tagits fram med två ECC-skyddade FIFO-moduler (se Fig 3), som ofta används i FPGA- och ASIC-baserade System-on-Chip, demonstrerar processen.

Fig 2. Renesas och OneSpin Solutions har presenterat en artikel med titeln ” ISO 26262:2018 Fault Analysis in Safety Mechanisms” vid konferensen 2019 DVCon Europe i München. En kopia av artikeln kan erhållas efter kontakt med författaren på sergio.marchese@onespin.com

Fig 3. Säkerhetsmekanismer för hårdvara övervakar indata och utdata hos avsedda funktioner och genererar diagnostisk information, och i vissa fall även korrigerade utdata. Detta ECC-skyddade FIFO-exempel visar att partitionering av logiken till subdelar, inklusive aktiv och passiv SM-logik, inte är någon trivial uppgift.

Steget för säkerhetsanalys använder en säkerhetscentrerad process för hårdvarupartitionering som automatiseras med hjälp av Fault Contribution Analysis (FCA) App. Felmoder associeras med design-subdelar som är avgränsade av nyckelsignaler, såsom skyddade utdata för den avsedda funktionen och diagnostiska SM-utdata. Varje SM-subdel kan klassificeras till en av två kategorier: Dels aktiva om dess fel kan fortplanta sig den avsedda funktionens utdata (observationspunkter), och dels passiva om felen bara kan utbreda sig till diagnostiska SM-utdata (diagnostiska punkter).

Subdelarna bearbetas för att producera fellistor och attribut (t.ex. uppskattad kiselyta), som kan användas för felanalys och andra efterföljande steg. Det är värt att notera att steget med säkerhetsanalys är skalbart till större, komplexa enheter, och är därigenom fritt från brister hos felsimulering och normal formell teknologi.

Resultatet av steget för hårdvarupartitionering ger omedelbart konservativa uppskattade säkerhetsmätetal. Felsimulering eller formellt baserad felanalys kan bara användas för specifika subdelar, om de uppskattade resultaten inte uppnår mål-ASIL. Fault Propagation Analysis (FPA) App och Fault Detection Analysis (FDA) App automatiserar detta extra felanalyssteg, som i själva verket reducerar pessimismen hos de uppskattade mätetalen för att förbättra resultaten. FPA App hittar säkra fel, d.v.s. fel som inte kan orsaka några brott mot säkerhetsmålen eftersom de inte utbreder sig till säkerhetskritiska utdata. FDA App hittar fel som alltid detekteras och indikeras av någon SM.

Slutligen kan resultaten från felanalysen av varje subdel kombineras för att få fram säkerhetsmätvärden för hela SoC-kretsen. Detta steg är också automatiserat genom Hardware Metrics Computation (HMC) App.

Slutsats

Att uppfylla kraven i ISO 26262 är en utmaning. För att kunna bevisa att SPFM och LFM ger tillräckligt höga värden i förhållande till mål-ASIL kan det krävas en noggrann identifiering av residuella och latenta fel. Potentiella sådana fel i SM:ar kan behöva analyseras i detalj.

För beräkning av hårdvarans säkerhetsmätetal för en stor SoC med många SM krävs ofta manuell analys av experter samt felsimulering. Manuell analys är tidskrävande och förenad med risker för fel. Felsimulering kräver avsevärda beräkningsresurser och en avsevärd mängd ingenjörsarbete för att utveckla en testbänk och rättfärdiga passande arbetsbelastningar.

Artikeln från Renesas och OneSpin introducerar en alternativ, skalbar metod för beräkning av säkerhetsmätetal för hårdvaran. Stora SoC-kretsar kan brytas ned till delar och subdelar med hjälp av verktyg för säkerhetsinriktad partitionering som kräver minimala insatser av användaren. Resultaten från felklassificeringen av subdelarna kan snabbt bedömas. Om konservativa bedömningar inte uppfyller målet kan en noggrann felklassificering användas selektivt. Här kan ingå identifiering av säkra, residuella och latenta SM-fel, med eller utan möjligheter till felkorrigering. En automatiserad, noggrann felklassificering kan utföras utan någon testbänk eller felsimulering med hjälp av formellt baserad teknologi.

Idag är stora organisationer som erbjuder SoC- och halvledarkretsar för fordonstillämpningar ofta beroende av interna verktyg för att kunna förbättra sina utvecklingsflöden. Mindre och nystartade företag kämpar med att uppfylla säkerhetskraven eftersom de behöver fokusera sina investeringar på sina unika kompetenser och kan ha svårt att anställa säkerhetsexperter.

Fordonsindustrin behöver mogna och lättanvända EDA-lösningar som drar nytta av det bästa kunnandet hos ett antal företag och IC-projekt, detta för att kunna reducera kostnaderna för säkerhetsarbetet och behovet av experter. Den lösning som presenteras i DVCon Europe-artikeln behandlar dessa utmaningar. För att läsa mer om detta och beställa en kopia av artikeln, gå till onespin.com/fmeda.

Jörg Grosse och Sergio Marchese, OneSpin Solutions

Filed under: Fordonselektronik