IEDM speglade dagens halvledarforskning

IEEE International Electron Devices Meeting (IEDM) räknas med sina internationella föredrag inom områdena mikro- och nanoteknik samt bioelektronik som en av de främsta fackkonferenserna i världen. I början av december träffades toppexperter inom dessa områden för 58 gången i San Francisco.

Vår amerikanske korrespondent Henning Wriedt rapporterar här från några av de intressantaste bidragen på IEDM.

På konferensen presenterades inte bara uppseendeväckande framsteg inom mikro- och nanoteknologi, såsom minnen, material och logikelement, utan också inom områden som energiskördande, effekthalvledare och biomedicinska komponenter. Konferensen kan i viss mån ses som en kristallkula, där man kan få en förutsägelse av den kommande teknologiutvecklingen.

22 nm tri-gate för SoC

Krympandet av transistorer stöter idag på enorma problem, som experterna försöker komma förbi genom innovativa ansatser inom transistorarkitekturer. Ett lovande område är multi-gate-transistorer, som har goda switchningsegenskaper och hög strömtålighet även vid låga matningsspänningar.

Intel presenterade sin version av multi-gate-teknologi i form av en komplett, mångsidig och tredimensionell 22 nm Tri-Gate-plattform för SoC-applikationer. De extremt snabba transistorerna har läckströmmar i området 100 nA/µm till 1 nA/µm, medan lågeffektsversionerna kommer ner under 50 pa/µm. De motsvarande drivströmmarna är trots detta omkring 50 procent högre än hos de traditionella 32 nm planarversionerna.

Tillverkningsprocessen kan dock även ge högspänningstransistorer (1,8 eller 3,3 V) för analogkretsar, I/O och äldre konstruktioner. De erbjuder dessutom de högsta I/O-drivströmmarna (NMOS/PMOS = 0,92/0,8 mA/µm vid 1,8 V).

Tri-Gate-teknologiplattformen består bl a av elva skikt med low-k och ultra-low-k CDO-förbindningar (Carbon-Doped Oxide) med små avstånd. Den möjliggör många olika analog/blandsignalslösningar och tre olika SRAM-bitceller med låga läckströmmar och hög täthet (0,092 till 0,130 µm²).

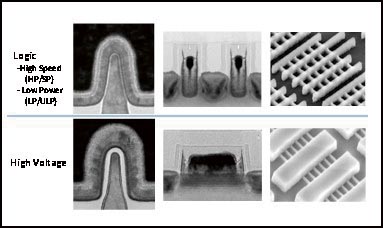

Fig 1 visar TEM-fotografier av Fin- och Gate-strukturer, liksom SEM-fotografier på en tunn logikgrind (överst) och den ”tjocka” högspännings-gaten hos en transistor.

Fig 1. TEM-fotografier visar Fin- och Gate-strukturer och SEM-fotografier visar en tunn logikgrind (överst) och den ”tjocka” högspännings-gaten hos en transistor.

(Källa: Intel)

22 nm CMOS i hybridteknik

CMOS-teknologin använder två olika MOSFET-transistorer (N och P), som samarbetar komplementärt med varandra. Motstridiga materialegenskaper och konstruktionskrav gör det dock svårt att uppnå balanserade prestanda och önskade spärrspänningar.

Samtidigt har ETSOI-teknologin (Extremely Thin SOI) visat sig vara en framgångsrik komponentarkitektur, som tillåter en kontinuerlig CMOS-skalning ända till 22 nm och lägre. Denna teknologi möjliggör en mycket noga kortkanalstyrning och har låg komponentspridning med odopade kanaler.

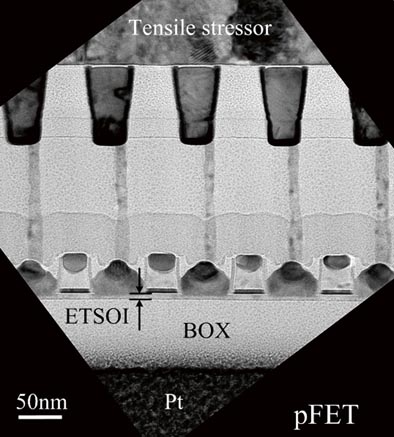

Under konferensen presenterade IBM världens första ETSOI CMOS-element i hybridkanalsversion. Forskarna har integrerat en PFET som har en tunn, uttöjd (”strained”) SiGe-kanal med en NFET som har en 22 nm Si-kanal. Denna hybridteknologi har möjliggjorts tack vare en speciell STI-last-process (isolation-last).

För att testa prestanda tillverkade forskarna en ringoscillator, som tack vare de hybrida planarelementen är den hittills snabbaste i världen med en fördröjning på bara 11,2 ps/steg vid 0,7 V. Detta är bättre än vad som uppnåtts t o m med FinFETar.

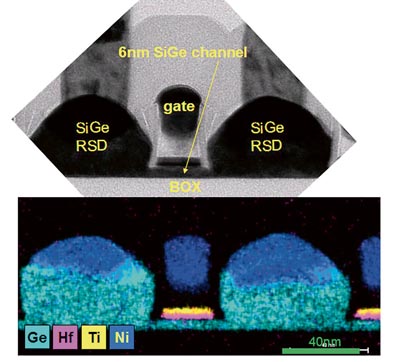

Fig 2 visar en PFET med en 6 nm bred SiGe-kanal. Gate-längden är bara 22 nm och gate-tätheten 100 nm.

Fig 2. Bilden visar en PFET med en 6 nm bred SiGe-kanal. Gate-längden är bara 22 nm och gate-tätheten 100 nm.

(Källa: IBM)

Germanium på kisel

För att förbättra FinFETarnas prestanda undersöker forskarna bl a material med hög elektronmobilitet. Germanium (Ge) passar av detta skäl mycket bra för kanalerna i P-transistorer, men det är mycket svårt att odla germanium direkt på kiselsubstrat. Hittills har man vanligen använt flera gränssnittsskikt med ökande Ge-koncentration, men detta har lett till oönskad komplexitet och höga kostnader.

TSMC beskrev ett mycket intressant alternativ: en heterogen epitaxial tillväxtsprocess som för första gången gör det möjligt att odla germanium direkt på kisel. Efter en noggrann processoptimering kunde forskarna slå fast, att om sidoförhållandet hos en fena uppgår till 1,4 eller mer kommer ”threading locations” att begränsas till Ge-Si-gränssnittet i fenans undre del. Den övre delen av fenan, d v s det aktiva området, förblir felfritt.

Man har demonstrerat denna teknologi med en komponent med excellenta egenskaper under tröskeln (branthet = 74 mV/dec), mycket god kontroll över kortkanaleffekten och höga prestanda (1,2 mA/µm och Vdd = 1 V). Detta öppnar vägen för ett fortsatt användande av germanium i framtida p-FinFETar.

Ambipolär nanotråds-FET

Fenomenet ambipolär ledning, d v s möjligheten att koppla om mellan p- och n-typ, har redan observerats i nano-transistorer i kisel, kol och grafen. Även om detta som regel inte är användbart i kretskonstruktioner vid 22 nm och därunder beslöt en grupp forskare vid École Polytechnique Fédéral de Lausanne (EPFL) att undersöka egenskapen närmare.

De byggde en ”gate-all-around”, ambipolär Si-nanotråds-FET i en vertikalt stackad konfiguration på ett SOI-substrat. I nanotrådens ändar placerades ”polaritetsgrindar”, som gjorde det möjligt att koppla om mellan n- och p-tillstånden, styrt med hjälp av en styrgrind i mitten.

Nanotråds-FETarna uppvisade ett mycket gott till/från-strömförhållande på 106 och en branthet under tröskeln på 70 mV/dec. En logikgrind med XOR-funktion byggdes för att bevisa den nya teknologins användbarhet.

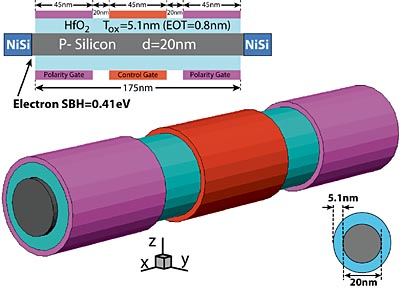

Fig 3 visar en datorsimulering av strukturen för en optimerad ambipolär kisel-nanotrån med tre 45 nm långa gate-regioner.

Fig 3. Denna datorsimulering illustrerar strukturen för en optimerad, ambipolär kisel-nanotråd med tre 45 nm långa gate-regioner.

Komplext 64 Mbit ST-MRAM

Konventionella, laddningsbaserade minnen håller på att närma sig gränsen för sin skalbarhet. Men samtidigt håller MRAM (Magnetoresistive Random Access Memory) på att utvecklas till en lovande efterträdare till dagens SRAM och DRAM.

I MRAM lagras data med hjälp av magnetiska ”moment”. Parallella och anti-parallella magnetiska moment i MRAM-stacken representerar tillstånden ”0” resp ”1”. I tidigare generationers MRAM skedde växlingen mellan dessa tillstånd med hjälp av ströminducerade magnetfält.

Detta har dock visat sig skapa problem vid skalning. Men genom uppfinnandet av ST-MRAM (Spin-Torque), där växlingen sker genom injektion av en spinpolariserad tunnelström, har man kommit förbi dessa skalningsproblem.

Forskare vid Everspin Technologies beskrev att man varit först med att tillverka ett fungerande 64 Mbit ST-MRAM med goda elektriska egenskaper. Detta visar att MRAM-teknologin nu står nära inför en kommersialisering.

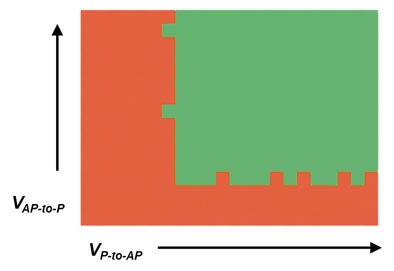

Fig 4 visar en s k ”shmoo plot”, som beskriver ST-MRAM-minnens prestanda vid olika spänningar. Det gröna området betyder felfri funktion och visar att minneskonceptet är robust.

Fig 4. Grafiken, en s k ”shmoo plot”, beskriver ST-MRAM-minnens prestanda vid olika spänningar. Det gröna området betyder felfri funktion och visar att minneskonceptet är robust.

(Källa: Everspin)

Horisontella kanaler i ultrasmå 3D-NAND

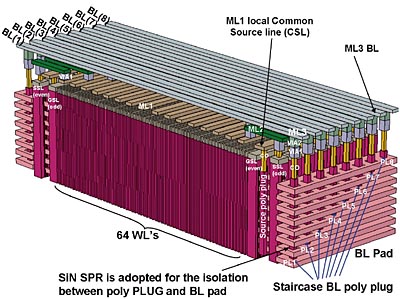

De första 3D-NAND-flashminnena med strukturer under 40 nm visades av experter från Macronix. De har använt vertikala grindar med horisontella kanaler för att få fram en ny arkitekturlayout som ger väsentligt mindre dimensioner i ordledningsriktningen och förbättrar tillverkningsprocessen.

I den nya arkitekturen kan man också använda speciella kontaktformationer (Staircase) för bitledningen, vilket minskar antalet tillverkningssteg och ger lägre kostnader. Resultatet är en åttaskikts komponent med ordledningsstrukturer på 37,5 nm, bitledningsstrukturer på 75 nm, 64 celler per rad och en kärnmatrisverkningsgrad på 63 procent.

Enligt forskarna är den nya teknologin inte bara mer kostnadsgynnsam än dagens sub 20 nm-strukturer, utan den ger också vid skalning till 25 nm en minneskapacitet på upp till 1 Terabit.

Fig 5 visar den föreslagna arkitekturlayouten för ett 3D-NAND-flashminne.

Fig 5. Föreslagen layoutstruktur för ett 3-D NAND-Flashminne.

(källa: Macronix)

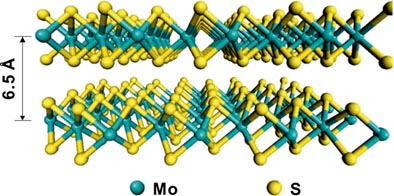

Molybdensulfid bättre än grafen?

Grafen, som består av en-atom tjocka blad av kolatomer, betraktas som en potentiell ersättare för kisel i framtida transistorer eftersom materialet uppvisar ytterst goda elektriska egenskaper. Men transistorer av grafen kan inte stängas av eftersom de saknar bandgap.

Detta har fått forskarna att söka efter nya 2D-material, t ex molybdensulfid (MoS). Detta material har egenskaper snarlika grafens, och därtill ett stort energibandgap.

Ett team från MIT beskrev under konferensen hur man med hjälp av CVD (Chemical Vapor Deposition) kan tillverka uniforma, flexibla och en-molekyl tunna MoS-skikt. Här befinner sig ett skikt med Mo-atomer mellan två skikt med S-atomer.

Genom att utnyttja materialets 1,8 eV stora bandgap har man tillverkat MoS-transistorer och enkla digitala och analoga kretsar (en NAND-logikgrind och en 1-bits A/D-omvandlare). Transistorerna uppvisade en hög mobilitet (>190 cm²/Vs), ett mycket högt till/från-strömförhållande (108), en rekordstor strömtäthet (omkring 20 µA/µm) samt för första gången högfrekvensprestanda i GHz-området.

Fig 6 visar gitterstruturen hos MoS.

Fig 6. Gitterstrukturen för molybdensulfid – ett material som är ett alternativ till grafen. MoS bandgap på 1,8 eV kan utnyttjas för att tillverka transistorer och dioder.

(Källa MIT)

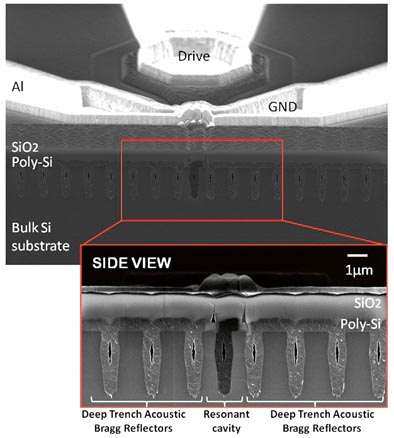

3,3 GHz MEMS-resonator i CMOS

En vanlig uppgift vid elektronikutveckling är att generera referensfrekvenser för timing- och kommunikationsändamål. Ett sätt detta kan göras på är att använda vibrerande mikromekaniska resonatorer. Men det är svårt att integrera MEMS-elementen i CMOS-kretsar. Ett av problemen härvid är att få bort dessa element från substratet efter tillverkningen, så att de kan integreras med CMOS-kretsen.

Detta problem hade ett team från MIT kommit runt genom att elektrostatiskt driva en MEMS-resonator försedd med djupa gravar som fungerade som kapacitanser. Resonansfrekvensen kunde enkelt bestämmas med hjälp av den litografi som användes för att tillverka gravarna. Gravarna fungerade också som akustiska Bragg-reflektorer, som minimerade resonansvibrationerna till storlek och utbredning.

MEMS-resonatorn, som arbetade på 3,3 GHz, tillverkades i en 32 nm SOI-process och uppvisade ett Q-värde på 2 057. Denna MEMS-integration i CMOS krävde inga extra tillverkningssteg.

Fig 7 visar mikroskopbilder av en resonator med djupa gravar.

Fig 7. Makroutförande av en resonator med djupa gravar.

(Källa: MIT)

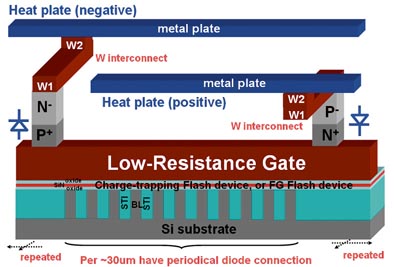

Självläkande flash lever längre

Flashminnen har en begränsad livslängd eftersom upprepade programmerings/raderingsoperationer (P/E) degraderar tunneloxiden som isolerar flashminnescellerna.

I princip går det att reparera skadorna genom upphettning av oxiden, men i praktiken går det inte eftersom flashminnena inte tål de höga temperaturer och långa upphettningstider som krävs.

Forskare vid Macronix rapporterade att de har byggt flashminnen som kan reparera sig själva med hjälp av små inbyggda värmegeneratorer som upphettar just de områden där det behövs. De modifierade ordledningen från en osymmetrisk till en symmetrisk struktur, genom vilken gate-strömmen kan flyta och generera värme. De höga temperaturerna (över 800 C) uppstod alltså bara i omedelbar närhet av gaten.

Komponenterna har uppvisat en livslängd på mer än 100 miljoner P/E-cykler med excellenta datalagringsegenskaper. Intressant nog kunde man konstatera att upphettningen också gav snabbare radering.

Fig 8 visar strukturen hos en ordledning

Fig 8. Strukturen hos en ordledning i ett flashminne.

(Källa: Macronix)

CMOS på flexibel tunn plast

Flexibla elektronikkretsar ger löften om ett stort antal nya produkter inom områden som biomedicin, säkerhet och elektronik integrerad i kläder. Tyvärr har flexibla kretsar hittills bara uppvisat begränsade prestanda, eftersom plastsubstraten inte klarar de höga temperaturer som krävs vid CMOS-tillverkning. Försök har gjorts att tillverka CMOS-kretsar på kiselsubstrat och sedan flytta över dem till plast, men detta har varit både komplext och kostsamt.

På konferensen berättade IBM en metod att komma runt problemet och demonstrerade avancerade CMOS-kretsar, däribland SRAM-minnen och ringoscillatorer, på flexibla plastsubstrat. De ytterst tunna ETSOI-kretsarna (extremely thin silicon on insulator) har en tjocklek på blott 60 Ångström.

IBM tillverkade dem på kisel och använde sedan en enkel och prisbillig process vid rumstemperatur, kallad ”kontrollerad spaltning” (controlled spalling), som man kan säga skalade bort kiselsubstratet. Kretsarna, med en gate-längd på mindre än 30 nm och ett gate-avstånd på 100 nm, överfördes sedan till plastsubstratet. Ringoscillatorn uppvisade en fördröjning på bara 16 ps per steg vid 0,9 V. För en flexibel krets är detta ett mycket gott resultat.

Fig 9 visar ett tvärsnitt genom substratet efter selektivt avlägsnande av kiselrester. Elementets strukturella integritet har bibehållits.

Fig 9. Tvärsnitt i substratet efter selektivt avlägsnande av kiselrester för att skapa CMOS på flexibel, extremt tunn plast.

(Källa: IBM)

Henning Wriedt

Filed under: Halvledarteknik