Fujitsu halverar energiförbrukningen för SRAM

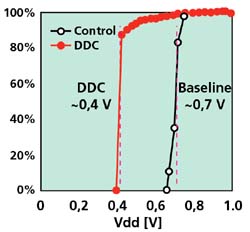

På IEDM-konferensen demonstrerade Fujitsu Semiconductor idag ett SRAM med matningsspänning ner till 0,425 V. Det innebär en dramatisk sänkning av energiförbrukningen, ner till mindre än hälften av vad som är möjligt idag.

Yield för ett 576 kbit SRAM

Förbättringen baseras på USA-företaget SuVoltas PowerShrink-plattform, där man med mycket små förändringar i en vanlig "bulk"-CMOS-process dramatiskt kan minska spridningen i transistorernas Vt. Genom att genomföra de här förändringarna på Fujitsus vanliga lågeffektsprocess har man i det närmaste kunnat halvera SRAM-cellernas matningsspänning, utan att få problem med dataförluster eller minskad hastighet.

På senare tid har det varit mycket svårt att minska energiförbrukningen ytterligare för minneskomponenter. Orsaken är att transistorernas spridning varit så stor att en sänkning av matningsspänningen under 1 V lett till förluster av data. Detta trots att processgeometrierna minskats från ca 130 nm till ca 28 nm.

SuVoltas DDC-teknik (Deeply Depleted Channel) minskar variationerna dramatiskt och gör det därför möjligt att minska matningsspänningen. Och med tanke på att minskningen i effektförbrukning i princip är kvadraten på spänningsminskningen blir de möjliga effektvinsterna mycket stora, från en halvering och neråt.

På IEDM-konferensen i Washington visade de bägge företagen att ett 576 kbit SRAM i 6T-teknik kan fungera säkert vid ca 400 mV matningsspänning. Detta med en traditionell 65 nm CMOS-process, utan 3D-strukturer (FinFET) eller SOI-teknik (kisel på isolator). FinFet eller ETSOI har annars av många ansetts som krav för att komma vidare till bättre halvledarprestanda. Detta trots att de bägge teknikerna är komplexa, dyra och kräver stora förändringar i processinfrastrukturen.

Filed under: Utländsk Teknik