Återinföra felanalys ger nya möjligheter med ISO 26262

Felsimulering har varit problembarnet vid ISO 26262-analys inom fordonsområdet ända sedan standarden publicerades år 2011. Metoden är hämtad från halvledartillverkarnas värld. Men traditionell felsimulering har aldrig varit någon idealisk metod för att få fram kritiska mätresultat för ISO 26262. Simuleringen kan ibland sträcka sig över månader vid de enklaste fel, och för att uppnå hög täckningsgrad har det krävts detaljerat arbete med stora risker för att göra fel.

Den nya generationen av verktyg för felanalys, som förkortar veckor av simulering till timmar, har visat sig medföra en total förändring vad gäller utvecklingsschema och kvalitet. Möjligheten att köra sessioner med iterativ felanalys för att inrikta sig närmare på olika problem har också skapat nya, oväntade möjligheter. Transienta feltyper kan nu analyseras noggrannare, medan mer krävande botemedel bara behöver sättas in när det är nödvändigt. Täckningsexponeringen kan automatiseras för att förbättra både kvalitet och tidsschema. Nästa generations felanalys kan komma långt när det gäller att snabbare minska säkerhetsriskerna med halvledare.

ISO 26262 i praktiken

ISO 26262 Automotive Functional Safety Standard definierar specifika risktoleransnivåer som är nödvändiga för elektroniska enheter inom fordonsområdet. För att få den maximala värderingen ”ASIL-D” krävs en mycket hög toleransgrad. Denna specificeras som en FiT-faktor (Failure-in-Time) på mindre än 10 fel per miljarder timmars drift, och därtill kommer ett ”Single Point Fault Metric” högre än 99 % och ett ”Latent Fault Metric” (LFM) högre än 90 %.

För att kunna garantera att en enhet uppfyller dessa stränga mål sätts säkerhetsmekanismer in för att eliminera de allra flesta av de slumpmässiga fel som naturligt uppstår när enheten är i drift. Feltoleransen hos enheten måste testas före tillverkningen för att garantera att dessa säkerhetsmekanismer gör sitt jobb. På ISO 26262-språk kallas detta för FMEDA-processen (Failure Mode Effect and Diagnostic Analysis). Den enda väg som finns idag för att mäta de nödvändiga felmåtten är att använda traditionell felsimulering.

Felsimulering ett hinder för utvecklingen

Felsimulering är en metod som uppfanns för omkring tre decennier sedan för att garantera testkvaliteten vid tillverkning. Principen är enkel. Först körs en simulering på en ren konstruktion med hjälp av testvektorer som tagits fram speciellt för detta syfte, och utsignalerna registreras. Ett fel (antingen ”stuck-at-1” eller ”stuck-at-0”) läggs in på en specifik designnod och simuleringen körs igen. Detta upprepas för samtliga noder i konstruktionen. Om utsignalen inte påverkas av felet kan testerna behöva förbättras, eftersom felet inte upptäcktes.

Naturligtvis var exekveringstiden för denna process – som i sin renaste form motsvarade antalet fel gånger storleken på simuleringen – enorm. Även efter optimeringar kunde simuleringstiden uppgå till veckor eller till och med månader.

Testning för fel inom fordonsteknik skiljer sig inte så mycket från testning vid tillverkning. I båda fallen måste fel injiceras, och enhetens reaktion härpå mätas. Därför var det ofrånkomligt att felsimulering borde vara det främsta valet för ISO 26262-karakterisering. Men det finns viktiga skillnader som gör den äldre teknologin olämplig.

Tester vid tillverkning var t.ex. ”scan-path”-baserade, vilket betyder att ett test bara behövde exekveras från en vippa, genom logik, till en annan vippa. Säkerhetstester, å andra sidan, måste trigga ett fel, och sedan mäta dettas inverkan genom flera klockade vippsteg innan det kommer fram till en säkerhetsmekanism eller en utgång. Detta gör testprocessen mycket längre och mer tidskänslig till sin natur. Den typ av fel som skall mätas kan inte bara approximeras med ett enkelt ”stuck-at-1” eller ”stuck-at-2”, som inom tillverkningsvärlden. Det betyder att simulatorn måste arbeta med nya felmodeller, som exempelvis transienta fel.

Tillverkarna av halvledare till fordonsindustrin kommer ofrånkomligen försöka att uppfylla kraven i ISO 26262 med ett minimalt antal felsimuleringar. Några företag kommer att köra simuleringar på små block, och sedan visa hur de mätresultat man fått fram kan överföras upp till den bredare systemnivån. Andra kan tänkas utföra statisk analys på resultaten för att visa att det är en rimlig sannolikhet för att en enhet är säker. Med tanke på denna marknads storlek och konkurrenssituation är det ofrånkomligt att förbättrade metoder för felanalys kommer att införas.

Nästa generations utveckling inom fordonsteknik

I takt med att fordonselektroniken blivit allt mer sofistikerad, och dessutom kommit att användas som en viktig källa för differentiering och värdeökning av själva fordonet, har marknaden för dessa komponenter exploderat. Detta har gjort att specialiserade utvecklingsinsatser nu satsats på sådana verktyg som krävs för att kunna förbättra verifieringen av säkerheten.

Som exempel på dessa nya verktyg och metodiker finns Test Suite Synthesis, Formal Verfication och förbättrad Fault Analysis. Test Suite Synthesis ger möjligheter att producera tester baserade på scenariespecifikationer, vilket drastiskt ökat täckningsgraden. Formal Verification har använts för att renodla och optimera de fellistor som måste analyseras av felsimulatorn för att minska den totala simuleringsbördan. Båda dessa utvecklingar är ytterst viktiga och värdefulla.

Men riktiga framsteg kan bara uppnås om man byter ut det fundamentala verktyget i det totala flödet, nämligen felsimulatorn. Nya metoder för felanalys, sådana som de från Optima Design Automation, har tagits fram för att ersätta felsimulatorn med en maskin som optimerats direkt för fordonsspecialiserad felanalys och som ger en faktor tio högre acceleration jämfört med tidigare metoder.

Nya lösningar för felanalys är inriktade på de fordonsspecifika kraven i ISO 26262, vilket eliminerar bearbetning av onödiga kvarlevor från tillverkningsinriktad felsimulering. De arbetar med separata optimeringar som använder metoder som ”pruning” och ”collapsing” av fel, tillsammans med parallell databearbetning. Dessutom utnyttjar de algoritmer för formell verifiering och prestandasimulering för att producera en helt ny motor som kan ge stora prestandaförbättningar.

Genom att felsimuleringsprocessen accelererats går det att snabbare beräkna FMEDA-resultat som baseras på hårda ”stuck-at-1/0”-fel. För Optima handlar det om en förbättring med en faktor tio eller mer. Dessutom kan ”fellistan” (de fel som måste undersökas) optimeras med hjälp av ett antal algoritmer. Med formella metoder kan denna lista skäras ner baserat på vilka följder ett feltillstånd kan ge, liksom på mer standardiserade metoder som sammanslagning av fel. Detta snabbar upp exekveringen ytterligare.

Allt detta medför att felsimulering för den befintliga FMEDA-processen kan utföras på några timmar, snarare än på några veckor. Härigenom blir det möjligt att reducera statistiska approximationer till feltolerans på systemnivå, och istället utföra exakta mätningar. Det går också att försöka med olika alternativ med olika säkerhetsmekanismer och försöka att optimera själva konstruktionen med avseende på effektförbrukning och prestanda, men fortfarande behålla ASIL-D-tolerans.

Något som är viktigt med FMEDA-processen är att följa upp och förbättra täckningsgraden. Att förbättra feltäckningen kan vara en mödosam och tidskrävande aktivitet som omfattar justering antingen av testvektorerna eller av själva konstruktionen. Med en förbättrad felanalys går det att effektivt använda olika metoder för inspektion av täckningen. Detta ger möjligheter till automatiserade förbättringar av täckningsgraden.

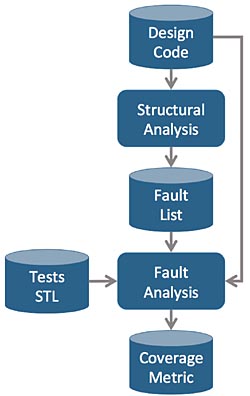

Fault Analysis Process

Förverkliga nya möjligheter inom fordonssäkerhet

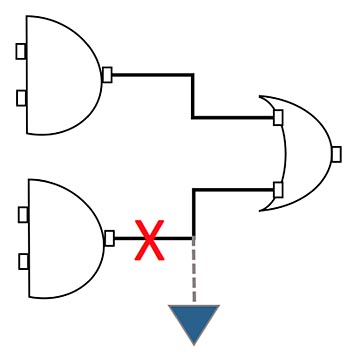

Med traditionell felsimulering kan bara de mest elementära feltillstånd (”stuck-at-1/0”) analyseras. Men mer komplexa fel kan också orsaka avbrott, och dessa måste också hanteras på lämpligt sätt.

Stuck at 0 fault insertion

Transienta fel kan om de uppstår vid fel tidpunkt på fel signal vara lika katastrofala som permanenta fel. Den ideala säkerhetsmekanismen för att fånga upp sådana fel är vippor som ”härdats” med hjälp av en metod kallad Triple Modular Redundancy (TMR). En ensam vippa ersätts här av tre vippor. Utsignalerna från dessa jämförs, och om en av dem ger ett avvikande resultat antas denna vara felaktig och de båda andra används för att ge den korrekta signalen.

Problemet med härdning av vippor är att storleken och effektförbrukningen hos vipporna ökar drastiskt. Om det inte går att noggrant bedöma vilka vippor som skall härdas – med hjälp av selektiv förstärkning – kommer ett stort antal av dem att ändras. Detta kommer att ge avsevärt försämrade prestanda och ökad effektförbrukning hos hela den aktuella enheten. I de flesta konstruktioner kommer somliga vippor bara att uppdateras under en liten bråkdel av klockcyklerna (t.ex. kontrollregister), eller också utför de inte några kritiska funktioner. Andra utför nyckelfunktioner eller uppdateras vid varje klockcykel (t.ex. datavägsregister).

För att beräkna det potentiella FiT-värdet (Failures in Time) hos en konstruktion som kan tänkas uppvisa transienta fel under drift, måste man ta fram ett stort antal tester som utsätter en specifik vippa för ett stort antal olika transienta feltyper. Därigenom går det att mycket noggrant bestämma vippans arkitektoniska sårbarhetsfaktor (Architectural Vulnerability Factor – AVF). Genom att sammanställa AVF för alla vipporna går det att göra en uppskattning av FiT-värdet.

Dessa algoritmer kräver att felsimulering körs på varenda vippa med olika belastningar, och därför har det inte varit möjligt att utföra denna process för ”selektiv härdning” förrän nu. Avancerad felanalys, tillsammans med andra metoder, gör att ett tillräckligt antal iterationer kan utföras för att genomföra denna analys och generera lämpliga mätvärden och konfigurationen för den idealiska härdade vippan.

Genom den förbättrade metodiken för kärnverifiering blir det möjligt att utföra många nya säkerhetskontroller och lösa andra viktiga problem. Det går också att utföra säkerhetsanalys med vissa av dessa metoder.

Transient Fault Analysis Process (klicka för större bild)

Sammanfattning

Vi ser nu en ny generation av AI-kretsar för förarlösa fordon, och dessa kraftfulla och komplexa halvledare kräver en helt ny designmetodik. Det handlar inte bara om att maximera säkerheten, utan det är också nödvändigt att revolutionera hela integriteten hos dessa konstruktioner. Avancerad felanalys spelar en huvudroll i denna nya ansats och kommer att bli centrum för nästa generations designmetodiker inom fordonsområdet.

Jamil Mazzawi, CEO, Optima Design Automation

Dave Kelf, Board Advisor, Marketing, Optima Design Automation

Filed under: EDA, Fordonselektronik