Kamerabaserad systemdesign del 4 – bygga ett inbäddat kamerasystem

I de tidigare artiklarna i den här serien beskrivs sensorurval i ett inbäddat kamerasystem och hur funktionsblocken kan implementeras i ett system som kombinerar en högpresterande processor och FPGA-struktur.

I den här artikeln visar Giles Peckham från Xilinx och Adam Taylor, CEng FIET, hur du skapar ett inbäddad kamerasystem med hjälp av Avnet MicroZed Embedded Vision Kit (EVK), som innehåller Python 1300C CMOS-bildsensorn på halvledare och Xilinx Zynq 7020 programmerbart SoC.

Python 1300C är en färgsensor med 1 280 bildpunkter x 1 024 rader, konfigurerad över ett SPI-gränssnitt. Dess seriella utdata möjliggör hög bildfrekvens, medan EVK ger ett HDMI-gränssnitt till en skärm.

Zynq 7020 implementerar systemets funktionalitet, med FPGA-strukturen (programmerbar logik, eller PL) för att implementera enhetens gränssnitt och bildbehandlingskedja. Dubbla ARM A9-kärnor driver Zynqs processorsystem (PS), som kan användas för systemövervakning och, vid behov, för förlängning av bildbehandlingskedjan.

Bygga maskinvaran

Två SoC-utvecklingsverktyg används: Xilinx Vivado 2015.4 och Xilinx SDK 2015.4. Vivado används för att implementera enhetens gränssnitt och bildbehandlingskedjan. Det används också för att konfigurera PS inom Zynq och minnesmappad PS-till-PL-kommunikation för att konfigurera IP i bildbehandlingskedjan efter bildstorlekar, bildfrekvens och önskade åtgärder. Detta uppnås med den allmänna AXI-anslutningen mellan PS och PL, med PS som huvudkomponent.

Vivado-verktyget används även för att placera processorns DDR-minne inom bildbehandlingskedjan så att processorn kan komma åt det om det behövs. Detta kan göras med den högpresterande AXI-anslutningen mellan PL och PS, där PL är huvudkomponenten.

Den här demonstrationen matar ut bilden till en skärm via HDMI, med enhetsgränssnittets IP-modul för Python 1300C och HDMI-utgångens IP-modul som gränssnitt mot HDMI-utmatningsenheten på EVK. Dessa IP-moduler ingår i satsen.

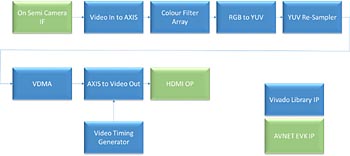

Bildbehandlingskedjan har ett gränssnitt till Python 1300C och utför funktionerna som visas i figur 1. Alla IP-kärnor som används ingår i Vivados standardbildbehandlings-IP-bibliotek, utom IP-kärnorna för Python 1300C och HDMI. Namnen på kärnorna och de funktioner som de utför anges nedan.

* Video in till AXIS: Konverterar den parallella videon, och horisontella och vertikala synkroniseringar, från Python-gränssnitts-IP:t till en AXIS-ström med gränssnitt mot de bildbehandlande IP-kärnorna.

* Interpolering av färgfiltermatris: Gör att varje utdatabildpunkt tilldelas ett RGB-värde med hjälp av informationen från Bayermönstret som täcker indatabildpunkterna.

* RGB till YCrCb-färgrymdskonverterare: Konverterar färgrymden för att säkerställa utdata är i rätt format för HDMI-drivrutinen.

* Färgmättnadsomsamplare: Skalar YUV från 4:4:4- till 4:2:2-format.

* AXI VDMA: Konfigurerar en Video DMA för att överföra bildrutorna till PS DDR.

* AXI VDMA: Konfigurerar samma Video DMA för att läsa bildrutor från PS DDR.

* AXIS till Video ut: Omvandlar AXI-strömmen tillbaka till parallellt format.

* Videotidsinställningsstyrenhet: Tillhandahåller en tidpunktsreferensgenerator för tidsinställning av videoutdata.

Dessutom krävs två AXI-anslutningsmoduler för att systemet ska fungera korrekt. En behövs för den högpresterande AXI-anslutningen och den andra för den allmänna AXI-anslutningen, tillsammans med nödvändiga återställningsblock för varje klockdomän.

Bildbehandlingstillämpningar kräver ett antal klockdomäner, och de flesta kan uppfyllas med PL-strukturens klockor som tillhandahålls av PS inom Zynq. Den här tillämpningen kräver följande klockor:

* 108 MHz: bildpunktsklockfrekvensen för en bild som matas ut på 1 280 x 1 024 i 60 Hz.

* 75 MHz: för minnesmappad AXI och AXI Lite-gränssnitt.

* 150 MHz: för bildbehandlingskedjan, även kallat AXI-strömningsklockan. Den här måste vara minst lika med bildpunktsfrekvensen. En högre frekvens rekommenderas för att ha viss säkerhetsmarginal och minska buffringsbehovet.

* 200 MHz: referensklocka för Python 1300C-sensorn.

En klockguide används för att generera 108 MHz-bildpunktsklockan, eftersom den måste vara mycket noga inställd. 75 MHz och 150 MHz har en viss tolerans när de ställs in av PL-strukturens klockor, men 200 MHz-klockan kräver hög exakthet. Till skillnad från 108 MHz-klockan kan den genereras korrekt av PS-strukturens klockor.

Tabell 1 beskriver klockstrukturen för IP-modulerna som används.

Tabell 1. Klockstruktur (klicka för större bild)

Överlämna till programvaruutveckling

När utformningen har verifierats och adresser har tilldelats till minnesmappad kringutrustning som använder de högpresterande och allmänna AXI-anslutningarna (detta kan göras automatiskt) byggs maskinvaran in i Vivado 2015.4 och exporteras till programvaruutvecklingsmiljön SDK 2015.4.

SDK används för att konfigurera inte bara utformningen inom Zynq utan även vissa element på EVK, innan den används. Detta beror på att PS fungerar som systemets övervakare och styrfunktion i detta exempel. Därför måste hela det inbäddade kamerasystemet konfigureras.

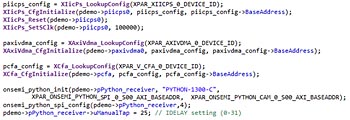

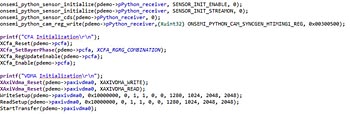

Vissa enkla programvaror behövs för att få igång systemet. I synnerhet används de för att konfigurera viktiga systemelement inklusive konfigurering av Python 1300C-kameran via dess SPI-gränssnitt, samt AXI Python 1300C-gränssnittsmodulen, AXI VDMA för att läsa från och skriva bildrutor till DDR-minnet, AXI-färgfiltermatrisen, HDMI-utdataenheten, I2C Mux och tillhörande kringutrustning och I2C I/O-expandern som styr strömskenorna för Python 1300C.

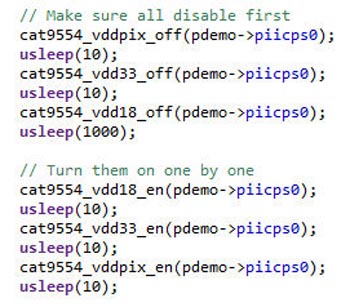

EVK använder Zynq PS I2C-styrenheten för att konfigurera HDMI-utdataenheten och aktivera strömförsörjningen till Python-enheten. Avnet tillhandahåller API:er för styrning av I2C och konfigurering av följande:

* ADV7511 – API för HDMI-utdata

* CAT9554 – API för I2C I/O-expandern på kameramodulen

* TCA9548 – API för I2C Mux på EVCC

* PCA9534 – API för I2C I/O-expandern på EVCC

* OnSemi_Python_SW – API för Python 1300C

* XAXIVDMA_EXT – API för konfigurering av VDMA

* XIICPS_EXT – API för körning av extern I2C

Utöver dessa API:er tillhandahålls även Xilinx API:er för IP inom bildbehandlingskedjan. För att skapa programmet laddas maskinvarukonstruktionen in till SDK och ett kretskortsupportpaket (BSP) skapas för denna maskinvara. Detta BSP innehåller alla Xilinx API:er som behövs vid sammankoppling med Avnet API:erna för att köra maskinvaran i bildbehandlingskedjan och Zynq.

Programvaran i sig krävs för att initiera AXI-kringutrustningen, strömsätta bildsensorskenorna och konfigurera Python 1300C, färgfiltermatrisen och VDMA. Vissa kodexempel visas.

Om man slutför dessa steg när programvaran körs på EVK leder detta till att en bild matas ut på HDMI-skärmen enligt figur 2.

* Initiera all AXI-kringutrustning

* Strömsätt bildsensorskenorna

* Konfigurera Python 1300C, färgfiltermatrisen och VDMA

Figur 2. Bildruta från en scen tagen med demot.

Sammanfattning

Efter artiklarna där delarna i ett inbäddat kamerasystem diskuterades visar den här demonstrationen hur ett system är byggt med programvaru-API:er och IP-bibliotek. Från den här startpunkten kan anpassade algoritmer sedan utvecklas och lägga till ytterligare värde till bildbehandlingskedjan.

Mer information finns på Microzed Chronicle-bloggarna och AVNET Git HUB.

Giles Peckham, Xilinx, Adam Taylor, CEng FIET

Filed under: Embedded