DSP för artificiell intelligens

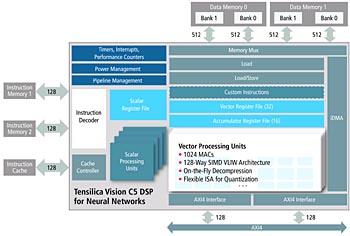

Cadence Tensilica Vision C5 är inte en accelerator, utan en komplett DSP-arkitektur för att hantera alla lager i en neuronnätsapplikation. Så mycket som möjligt skall kunna göras i ett chip och allt är optimerat för att minimera energiförbrukningen. På det här sättet hoppas Cadence kunna kapa åt sig en stor del av lågenergimarknaden för artificiell intelligens.

Klicka för större bild

Artificiell intelligens för mobiltelefoner, drönare och andra lågenergitillämpningar kräver nytänkande. Så lite som möjligt av energiförbrukningen bör gå till minnesaccesser och ”allmän hantering” och så mycket som möjligt till verkligt arbete.

Samtidigt är tekniken såpass omogen att man knappast kan starta från ”scratch”. Det ställer för stora krav på mjukvaran och innebär för stora risk att låsa in sig i en helt egen teknik. I det läget är signalprocessorn en rimlig utgångspunkt.

Tensilica har en stor fördel i sammanhanget. Företaget var ett av de första att satsa på konfigurerbara processorer och man har haft gott om tid att vidareutveckla sina verktyg för att skapa VLIW-baserade processorer och DSPer. Ganska tidigt visade det sig att de flesta användarna vill ha ett antal grundarkitekturer att utgå ifrån och sedan många år finns ett antal grundarkitekturer som kan byggas ut efter användarens behov. Genomgående för alla är de mycket breda instruktionerna och den mycket låga energiförbrukningen.

Artificiell intelligens

Att basera hårdvara för artificiell intelligens på DSP-teknik har stora fördelar. I grunden handlar det mesta om multiplikationer och det gäller att kunna göra så många som möjligt till så låg kostnad i form av energiförbrukning som möjligt. Det innebär heltalsmultiplikationer och möjlighet att variera precisionen efter behovet. Vision C5-arkitekturen klarar upp till 1 TMAC/sec och en implementering med en enda VLIW-processor räcker för ganska avancerade övervakningsändamål.

För ADAS-tillämpningar krävs ytterligare en nivå av prestanda, men också det kan hanteras med Vision C5. Arkitekturen går bra att parallellisera för att nå mycket höga prestanda.

Alla lager

Men den stora skillnaden mellan Vision C5 och traditionell AI-hantering med DSP är att Vision C5 är konstruerad att klara både de traditionella DSP-uppgifterna och de uppgifter som normalt sett hanteras av en generell huvudprocessor. Fördelen med det är framför allt att man kan minimera extern kommunikation och minnesaccesser. Här ligger en stor del av energiförbrukningen och här finns de största besparingarna att göra.

Vision C5 skall alltså klara alla lager i en neuronnätsapplikation på egen hand. Den är inte en hårdvaruaccelerator, utan en komplett AI-processor. Arkitekturen är en 128-vägs SIMD-VLIW-arkitektur med en rad vektorprocessorer, t ex upp till 1024 MAC-enheter. Två dataminnesenheter har upp till fyra 512 bit breda bussar och instruktionsminnet hanteras via tre 128 bit breda bussar. Ändå går det att implementera en Vision C5-enhet i bara 1 mm² kiselarea (14 nm).

IP

Det är viktigt att komma ihåg att Cadence inte säljer några komponenter baserade på varken Vision C5 eller andra av företagets arkitekturer. Allt handlar om IP (Intellectual Property) och det är komponenttillverkare och systemtillverkare som kommer att tillverka Vision C5-baserade lösningar, på samma sätt som företagets övriga DSP-lösningar för t ex audio och video.

Till att börja med räknar Cadence Tensilica på att sälja in Vision C5 i AI-tillämpningar med extrema krav på låg energiförbrukning. Typiska produkter är mobiltelefoner, övervakningskameror, drönare och fordonstillämpningar. Men på sikt är det också fullt möjligt att nå tillämpningar med bättre tillgång till energi. Trots allt innebär ju en halverad energiförbrukning en möjlighet att stoppa in dubbelt så höga prestanda vid en given energibudget. Med 1 TMAC/sec per processorkärna och möjlighet att parallellisera ett ganska stort antal kärnor blir maximala prestanda mycket höga.

Filed under: Utländsk Teknik