50 år med DAC

Valet av Austin, Texas, som arrangör för årets Design Automation Conference var en fullträff. Området (The Silicon Hills) har de senaste åren utvecklats till en grogrund för innovationer, där mer än 4000 teknikföretag med cirka 100 000 anställda har samlats. Det är idag landets näst största teknikkluster.

Austin Texas Skyline

I nära samråd med lokala teknikföretag, skapade arrangörerna också ett mycket brett och högaktuellt konferensprogram, med nästan 300 presentationer, med inte bara klassiska DAC-ämnen som hård- och mjukvaruutveckling, utan också mycket annat. Den som hade energi över kunde också besöka de ca 200 EDA-företagen som ställde ut.

Keynotes med tekniska trender

Gregg Lowe, vd och koncernchef för Freescale Semiconductor med säte i Austin, öppnade serien av sex inledningsanföranden på temat "Embeddedprocessing – motorn bakom Internet of things". Enligt Lowe är embeddedprocessorlösningarna de grundläggande drivkrafterna för den omdiskuterade "Internet of Things", med ett nätverk utformat för att göra vårt liv enklare, säkrare och mer produktivt. Halvledartekniken kommer att fortsätta att tänja gränserna mot integration av heterogena arkitekturer i system-in-package.

Dr James Truchard, VD och koncernchef för National Instruments, också baserat i Austin, fortsatte med en presentation om vikten och de stora fördelarna med plattformsbaserad design i utvecklingen av heterogena system med multiprocessorer och FPGA. Dr Namsung Woo, vd för Samsung Electronics och ansvarig för LSI-verksamheten, tog i sin tur upp aktuella tekniker som TSV, FinFETs och kapsling av 3-D-chip. Med den snabba tillväxten av mobila applikationer och smarta handhållna enheter fokuserar EDA-samhället, enligt Woo, på att ta fram teknik för mycket låg strömförbrukning. Resultatet är bland annat applikationsprocessorer som kräver mycket mindre energi än traditionella processorer. Woo påpekade också att samarbetet mellan flera områden på Samsung Semiconductor leder till unika synergieffekter.

SoC-design är ett komplext samspel

Att konstruera systemkomponenter för mobil kommunikation är enligt Scott Runner från Qualcomm Technologies ett komplext samspel mellan kiselkonstruktion, effekt, programvara och verifiering, och det viktigaste är att använda effektiva metoder som t ex en optimerad samkonstruktion av hårdvara och mjukvara.

Sanjive Agarwala från Texas Instruments talade i sin presentation om den explosiva tillväxten av innehållsproduktion (content), distribution och konsumtion inom mobil kommunikation. Denna tillväxt kräver effektiva embeddedsystem från basstationens infrastruktur till "verksamhetskritiska" applikationer. Operatörerna av denna trådlösa infrastruktur kräver kostnadseffektiva lösningar för sin nätverksarkitektur för att möta konsumenternas krav idag och imorgon.

Talk of the Town: FinFET

Teknologiskalningen mot 14-nm och vidare nedåt innebär många nya utmaningar för halvledarkonstruktörer. I denna nya "värld" är FinFET-element, e-beam-litografi, och verifiering/konstruktion i 3-D av särskild betydelse. Yrkesverksamma från TSMC, imec, National Taiwan University och Synopsys beskrev de senaste aspekterna av den nuvarande tekniken.

Andra intressanta presentationer behandlade applikationsspecifik strömsnål konstruktion, minneskonstruktion med hög komplexitet MIMO-radiomottagare, högre effektivitet för inbyggda energimätsystem, säkerhetsaspekter hos system för medicinsk elektronik och konstruktion/felsökning med TLM (Transactional Level Model). Den sista dagen av DAC ägnades i huvudsak åt träning, med särskild tonvikt på SystemC, ARM Cortex och SystemVerilog. Utbildningen genomfördes av erfarna experter från Doulos och ARM.

Var klämmer skon?

En oskyldig besökare på DAC skulle kanske kunna tro att de olika EDA-verktygen redan löst de flesta aspekterna av halvledarkonstruktion. Men halvledarkonstruktörer vet bättre. Det finns många problem som aldrig har lösts och nya som uppstår.

Dr Robert Colwell från DARPA (Defense Advanced Research Projects Agency), gav i sin föreläsning ett antal rekommendationer som inte bör ignoreras. Således är RTL-validering och verifiering, enligt hans uppfattning en obestämd process – man kan aldrig bevisa att inga fel finns kvar i RTL-koden. Och även om du lyckas kan det mycket väl visa sig att beskrivningen är felaktig.

– Dessutom kan vi förvänta oss nya problem i området från 11 nm och nedåt. Då fungerar kisel inte längre så bra och bitfel kan lätt uppstå pågrund av överhörning, brus i strömförsörjningen eller kosmisk strålning. Hittills har hårdvarukonstruktörerna varit ganska bra på att dölja problemen, men under 11 nm blir det betydligt svårare.

– Kan mjukvaran vara räddningen? Kanske det – men då måste mjukvaran var med redan på RTL-nivån. Och vilken mjukvara? Runtimemjukvaran, operativsystemet eller applikationerna? Eller kanske alla tre.

– Det som vi verkligen värderar det kvantifierar vi också. Prestanda, effektförlust och chipstorlek hanterar vi i våra CAD-verktyg. Men vad är den grundläggande tillförlitligheten i en 2-in/1-ut NAND-grind vid 7-nm? Eller i en ledare? Eller i en 8-T SRAM-cell? Eller i en bit i ett register? Vi måste lära oss att kvantifiera tillförlitlighetsaspekterna vid halvledarkonstruktion.

Här nu följer nu kortfattade rapporter om nyheter sompresenterades under DAC.

IP-svit från ARM

ARM presenterade en optimerad IP-lösning för mobila enheter, med nya funktioner och bättre prestanda för att få lägre energiförbrukning och mindre kiselarea. Sviten utgår från ARM Cortex-A serien och grafikacceleratorn Mali-T, med Cortex-A12-processor och Mali-T622 GPU som bas, samt den nya acceleratorn Mali-V500. Tanken är att man med stöd av ARM POP-teknik och verktygssviten Studio 5 (DS-5) snabbare kan utveckla effektivare smartphones och surfplattor.

Cortex-A12-processor ger, jämfört med A9, en resultatförbättring på 40 procent vid samma energiförbrukning.

Mali-T622 GPU har OpenGL ES 3.0-stöd, OpenCL API och är förmodligen den minsta GPU-lösningen för mobila enheter.

Videolösningen Mali-V500 ger en dedikerad videolösning i hårdvara, vilket minskar kraven på systemets bandbredd med mer än 50 procent jämfört med nuvarande lösningar. Mali-V500 är en multicorelösning, som med en kärna klarar 1080p/60-kodning/avkodning och med flera kärnor klarar 4K Ultra HD med 120 bilder per sekund. Videolösningen stödjer också TrustZone-teknik.

Automation och tydlighet

Sage Design Automation (Sage-DA) grundades med målet att utveckla teknik och produkter som automatiserar regelbaserad design och verifiering.

Hittills har vi sett DRC-lösningar (Design Rule Check), det vill säga program som kontrollerar om den fysiska IC-konstruktion kan tillverkas, utan att kunna kontrollera riktigheten och exaktheten. Denna fråga blir allt svårare med nya processtekniker.

IDRM (Integrated Design Rule Management) från Sage DA presenteras här som en lösning där den nya tekniken snabbt och grafiskt detekterar komplexa konstruktionsregler så att kontrollen av en regeldefinition på en testlayout kan göras. iDRM ger halvledarkonstruktörer en klar och entydig regelbeskrivning

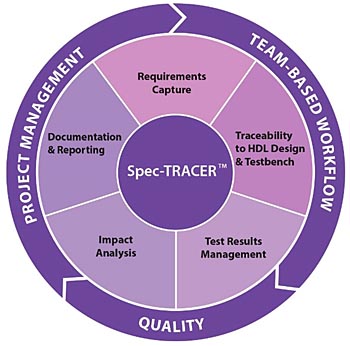

Spec-Tracer för säkerhetskritiska FPGA- och ASIC-konstruktioner

Aldec visade verktyget Spec-Tracer, en livscykellösning för säkerhetskritiska branscher där rigorösa standarder för certifiering är vanliga – som DO-254 i flygelektronik, ISO 26262 för fordonsindustri, IEC 61508/61511 för industri och IEC 61513 för kärnkraftsområdet. Hantering och dokumentering av FPGA- eller ASIC-konstruktioner, baserat på relevanta krav, är en alltmer komplex uppgift. Men det är nödvändigt för certifiering och produktion av tillförlitliga och säkra produkter.

– Spec-Tracer är precis vad flygelektronikbranschen behöver för att uppfylla kraven på spårbarhet enligt DO-254 krav, säger Louie De Luna, ansvarig för Aldecs DO-254-program.

Henning Wriedt fortsätter DAC-rapporteringen under sommaren

Filed under: EDA